# TMS320C24x PWM Simple Compare in Symmetric Mode

Application Report SPRA370

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

# **Overview**

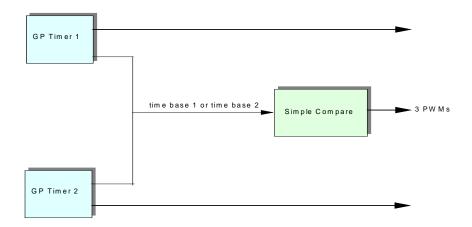

**Three simple Compare Units can generate up to 3 PWM**. The Time base for Simple Compare Unit is provided by the General Purpose Timer 1 or General Purpose Timer 2. The Simple Compare Module can be used in parallel with the Full Compare module and generate 3 additional phases with an independent time base. There is no possibility to generate complemented output with Simple Compare Output.

# Index

| 1. Possibilities of PWM Simple Compare in Symmetric Mode            | 4 |

|---------------------------------------------------------------------|---|

| 2. Description : Event Manager Programmation                        | 5 |

| 2.1 Simple Compare Unit Composition                                 | 5 |

| 2.2 Preparation Phase to Configure the Three Simple Compare Units _ | 6 |

| 2.3 Example                                                         | 6 |

| 2.4 Modification of the Active Width during Running                 | 9 |

# 1. Possibilities of PWM Simple Compare in Symmetric Mode

Simple Compare in symmetric mode can be used:

• To generate three symmetrical PWMs on the Simple Compare output

## 2. Description: Event Manager Programmation

Simple Compare Units connected to time base generation architecture

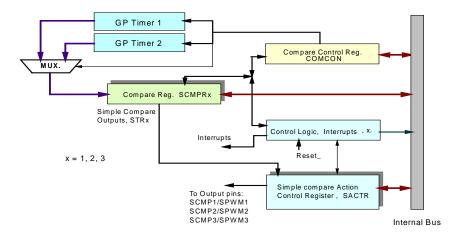

### 2.1 Simple Compare Unit Composition

#### 2.2 Preparation Phase to Configure the Three Simple Compare Units

Two main modules have to be programmed to generate three simple compare:

- Simple Compare Units programmation:

- to write SACTR : Action Control Register which controls the action on each of 6 compare output pins.

- to write SCMPR1 : Compare register 1

- to write SCMPR2 : Compare register 2

- to write SCMPR3 : Compare register 3

- to write COMCON : Compare Control Register

- Timer Base generation with General Purpose Timer 1: CF Application note "TMS320C24x General Purpose Timer 1 in symmetrical mode"

- to write TPR1 : Timer Period register.

- to write TCNT1 : Control register initialisation.

- to write TCON1 with bit 6=0b (timer disable)

- : Control register to program Count Mode Selection, Clock Pre-scaler, Clock Source, compare reload condition, enable compare operation.

- to write TCON1 with bit 6=1b to start the timer.

- : Control register to enable the Timer 1

#### 2.3 Example

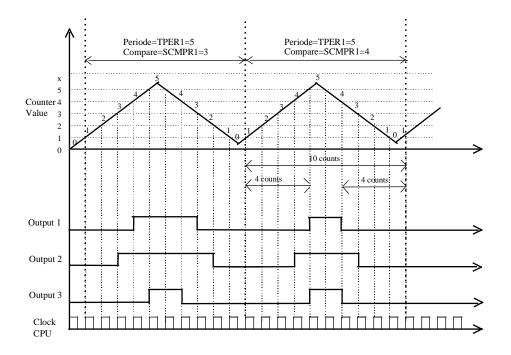

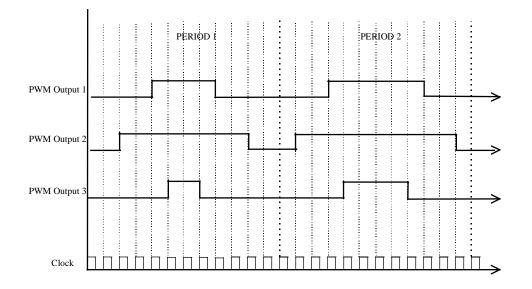

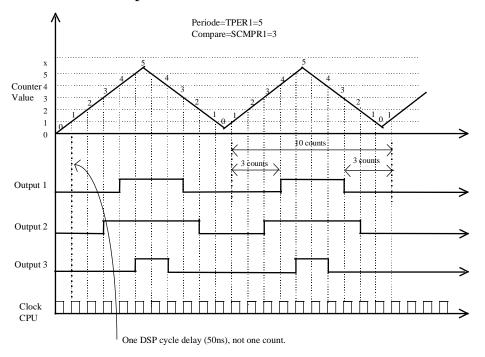

Generation of three symmetrical PWM.

- Free run, no emulation mode.

- Timer count mode Continuous Up/Down-Count Mode : symmetrical PWM.

- No timer input pre-scaler and internal clock.

- Reload the Simple Compare shadow compare register when counter equal 0.

- PWM output Active High for uneven output and Active Low for even output.

- Period 5 \* 2 \* 50ns.

Register programming:

SACTR = 2ah Bit 1&0 :10b ,Active High for output 1 Bit 3&2 :10b ,Active High for output 3

| SCMPR1<br>SCMPR2<br>SCMPR3 | =<br>=<br>= | Bit 5&4<br>3h<br>2h<br>4h   | :10b | ,Active High for output 5                                                                 |

|----------------------------|-------------|-----------------------------|------|-------------------------------------------------------------------------------------------|

| COMCON(1)                  | =           | 0100h<br>Bit 4&3<br>Bit 6&5 |      | ,Simple Compare action (SACTR)<br>,Simple Compare registers<br>reload condition : TCNT1=0 |

|                            |             | Bit 7                       | :0b  | ,Simple Compare time base<br>selects : GPTimer1                                           |

|                            |             | Bit 8                       | :1b  | ,Simple Compare output are enabled.                                                       |

| COMCON(2)                  | =           | 8100h<br>Bit 15             | :1b  | ,Enable Compare operations                                                                |

*CF* Application note "TMS320C24x General Purpose Timer 1 in symmetrical mode" for time base generation

|                | = 3h<br>= 0h |          |                                                                  |

|----------------|--------------|----------|------------------------------------------------------------------|

|                | Bit 1        | : 1b     | , 1                                                              |

|                | Bit 3&2      | : 00b    | operation.<br>, Compare Register reload<br>when counter is zero. |

|                | Bit 5&4      | : 00b    |                                                                  |

|                | Bit 6        | : 0b     |                                                                  |

|                | Bit 13,12&1  | 11: 101b | , Continuous-Up/Down Count<br>Mode.                              |

|                | Bit 15&14    | : 10b    | , GP timer not affected by emulation suspend.                    |

| TCON1 (second) | = a842h      |          | -                                                                |

|                | Bit 6        | : 1b     | , Timer 1 is enabled.                                            |

Initialisation Assembly code:

| GPTCON .set<br>TCNT1 .set | 7400h<br>7401h | ;General Timer Controls<br>;T1 Counter Register |

|---------------------------|----------------|-------------------------------------------------|

| TPR1 .set                 | 7403h          | ;T1 Period Register                             |

| TCON1 .set                | 7404h          | ;T1 Control Register                            |

| COMCON .set               | 740dh          | ;Compare Control Register                       |

| SACTR .set                | 740fh          | ;Full Compare Action Register                   |

| SCMPR1 .set               | 7414h          | ;Full Compare unit Compare register 1           |

| SCMPR2 .set               | 7415h          | ;Full Compare unit Compare register 1           |

| SCMPR3 .set | 7416h ;Full   | Compare | unit | Compare | register | 1 |

|-------------|---------------|---------|------|---------|----------|---|

| LDP         | #232          |         |      |         |          |   |

| SPLK        | #2ah,SACTR    |         |      |         |          |   |

| SPLK        | #3h,SCMPR1    |         |      |         |          |   |

| SPLK        | #2h,SCMPR2    |         |      |         |          |   |

| SPLK        | #4h,SCMPR3    |         |      |         |          |   |

| SPLK        | #100h,COMCON  |         |      |         |          |   |

| SPLK        | #8100h,COMCON |         |      |         |          |   |

| SPLK        | #5h,TPR1      |         |      |         |          |   |

| SPLK        | #0h,TCNT1     |         |      |         |          |   |

| SPLK        | #0a802h,TCON1 |         |      |         |          |   |

| SPLK        | #0a842h,TCON1 |         |      |         |          |   |

|             |               |         |      |         |          |   |

Result of this example

Note: the first period of a continuous up/down count is 1 DSP cycle longer and is not totally symmetrical (see diagram above).

#### 2.4 Modification of the active width during running

When new compare values in the Full Compare registers are written, new values are loaded in a shadow register and are active at the end of the period, when TCNT1=0 (for this configuration).

#### Example:

SCMPR1 switch from 3 to 4 during the second period SCMPR2 switch from 2 to 3 during the second period SCMPR3 stays at the same value

Results will be: