# TMS320 DSP DESIGNER'S NOTEBOOK **Obtaining Absolute Encoder Position on a TMS320C240**

APPLICATION BRIEF: SPRA279

David M. Alter Digital Signal Processing Products Semiconductor Group

*Texas Instruments July 1997*

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### CONTACT INFORMATION

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

## Contents

| Abstract       | 7 |

|----------------|---|

| Design Problem | 8 |

| Solution       | 8 |

|                |   |

# Figures

| Figure 1. Desired and Actual Encoder Number Sequencing for                        | •  |

|-----------------------------------------------------------------------------------|----|

| an 8 Count/Revolution Encoder                                                     | 9  |

| Figure 2. Binary number sequence of counter for a 2 <sup>n</sup> encoder with n=3 | 10 |

| Figure 3. Software rollover adjustment for a 9 count/revolution encoder           | 13 |

| Figure 4. Position Sequence After Sign Adjustment for                             |    |

| an 8 Count/Revolution Encoder                                                     | 16 |

# Examples

| Example 1. | Code Listing #1 | 11 |

|------------|-----------------|----|

| Example 2. | Code Listing #2 | 13 |

# Obtaining Absolute Encoder Position on a TMS320C240

### Abstract

Many servo applications require absolute position information as feedback. This document describes how the encoder count can be processed to obtain absolute position on the TMS320C240. The document includes a theoretical discussion, equations, timing diagrams and a lengthy code example.

### **Design Problem**

How can the encoder count be processed to obtain absolute position on the TMS320C240?

## Solution

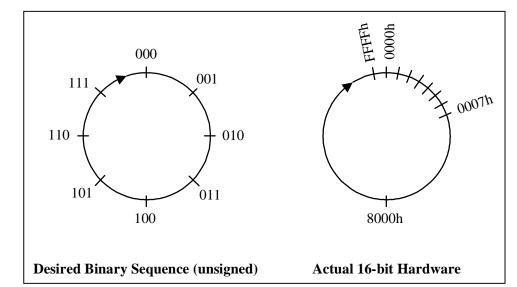

**General Issues:** Many servo applications require absolute position information as feedback. Two separate issues must be addressed when using an encoder sensor to obtain this. The first issue stems from a difference between the desired number sequence and the sequence implemented by the 16-bit counter holding the encoder count on the 'C240. Consider for example the sequence from an 8-count-per-revolution encoder, as shown in Figure 1. The hardware counter will only wrap at the FFFFh to 0000h boundary. However, the desired number sequence requires a wrap that corresponds to the number of counts per revolution, in this case 8h. Three methods to overcome this problem will be presented in this technical note.

The second issue involves obtaining absolute, rather than relative (i.e. incremental) position. Interpreting the position count sequence as absolute requires that it be referenced to some known physical encoder angle. This can be achieved in one of two ways. The first approach involves physically locking the encoder at some known angle during startup. A zero can then be written to the encoder counter register thereby referencing the position to the locked position. In permanent magnet motor applications, the entire process can be fully automated in software by statically activating one of the motor commutation paths and waiting for the rotor to rotate into position. This simple method has the advantage of not needing any additional hardware connections. The code required to perform this is straightforward although it does vary depending on the motor application and configuration. It therefore will not be discussed further in this note. The second approach relies on accurate knowledge of the physical angle at which the encoder is mounted. In this case, one can use the encoder index signal, which pulses once per revolution, to trigger a calibration procedure for the encoder count. Various implementations of this second method will be discussed in more detail in the following sections.

Figure 1. Desired and Actual Encoder Number Sequencing for an 8 Count/Revolution Encoder

#### Method 1: 2<sup>n</sup> encoder resolution

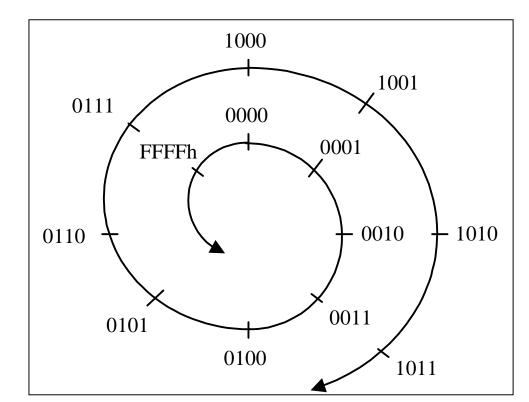

This method requires an encoder with  $2^n$  counts/revolution, where n is an integer. The key is to notice that the hardware counter will adhere to the desired number sequence in the least significant n bits of the count, as illustrated in Figure 2. Software must mask out the upper 16-n unwanted bits. The following code segment illustrates the process on the 'C240 using GP Timer 3 to hold the counts from an 8 count/revolution encoder (n = 3).

| T3CNT .set<br>.bss                 | 7409h ;GP Timer 3 counter register position,1 ;position variable                                                                            |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| .text<br>LDP<br>LACC<br>AND<br>LDP | <pre>#232 ;data page set to event manager<br/>T3CNT ;ACC = count<br/>#111b ;mask off unwanted upper bits<br/>#position ;data page set</pre> |

| SACL                               | position ;store position to memory                                                                                                          |

One can easily modify this code for more realistic encoder resolutions. For example, with a 1024 count/revolution encoder (n=10) the AND instruction should be changed to read AND #2ffh. An additional feature of this method is the ability to discriminate positions over more than one revolution by masking off fewer bits (e.g. 0 and 360 degrees will give different count values). This is often required in servo applications. For example, to obtain position over 2 complete revolutions of the example 8 count encoder, replace AND #111b with AND #1111b.

Figure 2. Binary number sequence of counter for a  $2^n$  encoder with n=3

The encoder index signal can be used to reference the absolute position by connecting it to one of the external interrupt pins on the DSP (e.g. XINT1, XINT2, or XINT3). During the startup sequence, the motor should be slowly rotated in some controlled fashion. When the index pulse triggers an interrupt, the GP Timer holding the encoder count is zeroed in the interrupt service routine (e.g. T2CNT or T3CNT registers). After zeroing, the external interrupt should be disabled (i.e. masked) so that calibration is only performed once. The position will now be referenced to the physical angle at which the index pulse occurred. Interrupt latency is normally not a problem. For example, a 1024-count encoder rotating at 1-revolution-persecond has 0.977 ms between counts. This allows for over 19,500 instruction cycles on a 20 MIPS DSP!

Methods 2 and 3 are presented next for non- $2^n$  encoder resolutions. Although they can be used with encoders of  $2^n$  resolution, they are inefficient when compared with method 1.

# Method 2: Non-2<sup>n</sup> encoder resolution, discrimination over a single rotation

This method can only discriminate position over a single rotation. The encoder index signal is connected to Capture #3, and the CAPCON register configured so that Capture #3 records the count of the GP Timer being used to hold the encoder count. This will occur once every 360-degree rotation of the encoder. In addition, the Capture #3 interrupt is enabled and its service routine is designed to copy the captured value off the CAP3FIFO results stack and store it in some data memory location (e.g. call it position ref). When the encoder count is processed, position ref is first subtracted from it. If the resultant is positive, processing is complete. If the resultant is negative, the number of counts per revolution should be added. These operations result in a desired number sequence similar to that shown in Figure 1 but with a different number of counts per revolution, and referenced to the index pulse position. Note that Capture #4 could be used instead of Capture #3 if desired. The following code segments illustrate the process on the 'C240' with the index signal connected to Capture #3, and GP Timer 3 holding the counts for a 9 count/revolution encoder.

| 1                                       | 0     |                                |            |                                                                                               |

|-----------------------------------------|-------|--------------------------------|------------|-----------------------------------------------------------------------------------------------|

| T3CNT<br>CAP3FIFO<br>EVIFRC             |       | 7409h<br>7425h<br>7431h        | ; C<br>; E | P Timer 3 counter register<br>apture #3 results stack<br>vent Manager Interrupt Flag<br>Reg C |

| <pre>position_ref count_rev</pre>       |       | position,2,<br>position+1<br>9 |            | <pre>;position ;position reference ;counts per revolution</pre>                               |

| * * * * * * * * * * * * * * * * * * * * |       |                                |            |                                                                                               |

| * Encoder Processing Code Segment       |       |                                |            |                                                                                               |

| *******                                 |       |                                |            |                                                                                               |

|                                         | .text |                                |            |                                                                                               |

|                                         | CLRC  | OVM                            |            | ;overflow mode off                                                                            |

|                                         | SETC  | SXM                            |            | ;use signed math                                                                              |

|                                         | LDP   | #232                           |            | ;DP set to event manager                                                                      |

|                                         | LACC  | T3CNT                          |            | ;ACC = count                                                                                  |

|                                         |       |                                |            |                                                                                               |

#### Example 1. Code Listing #1

off th nt manager LDP #position ;data page set ;subtract stored SUB position ref ; capture value ; branch if positive BCND STORE, GEQ ADD #count\_rev ;add counts per ; revolution STORE: SACL position ;store position to memory Capture #3 Interrupt Service Routine

| STATUS   | .usect | "BLOCKB2", 2            | ;must be located on<br>; data page 0 |  |  |  |

|----------|--------|-------------------------|--------------------------------------|--|--|--|

|          | .text  |                         |                                      |  |  |  |

| cap3int: | SST    | #0, STATUS              | ;save STO                            |  |  |  |

|          | SST    | #1, STATUS+1            | ;save ST1                            |  |  |  |

|          | LDP    | #232                    | ;DP set to event manager             |  |  |  |

|          | SPLK   | #0100b, EVIFRC          | ;clear CAP3INT flag                  |  |  |  |

|          | BLDD   | CAP3FIFO, #position_ref |                                      |  |  |  |

|          |        | ;save ca                | ptured value to data memory          |  |  |  |

|          | LDP    | #0                      | ;set data page                       |  |  |  |

|          | LST    | #1, STATUS+1            | ;restore ST1                         |  |  |  |

|          | LST    | #0, STATUS              | ;restore STO                         |  |  |  |

|          | CLRC   | INTM                    | ;global interrupts                   |  |  |  |

|          | RET    |                         | ;return                              |  |  |  |

Several points are worth noting about the code. First, the position obtained is inherently absolute in that it is always referenced to the index pulse absolute position. No further steps need be taken to provide for this. Second, the CAP3INT service routine performs the required context save-and-restore using direct addressing. Therefore, the uninitialized data section "BLOCKB2" must be linked to data page 0 since SST always saves to this page when using direct addressing. Also, the use of the BLDD instruction in the Capture #3 interrupt service routine rather than a LACC and SACL combination eliminates the need to context save and restore the accumulator. Finally, note that the encoder processing code segment of Method 2 is more computationally intensive than Method 1, although it is still arguably of negligible length. However, additional CPU cycles are needed once per revolution to execute the Capture #3 interrupt service routine.

# Method 3: Non-2<sup>n</sup> encoder resolution, discrimination over multiple rotations

Unlike method 2, this method can discriminate position over multiple rotations. The encoder is used in an incremental fashion, where the change in position from the last sample period is computed as the difference of the new count minus the old count, i.e.:

position = position + (new\_count - old\_count).

The old\_count is then replaced with the new\_count in preparation for the next sample period, i.e.:

`old\_count = new\_count.

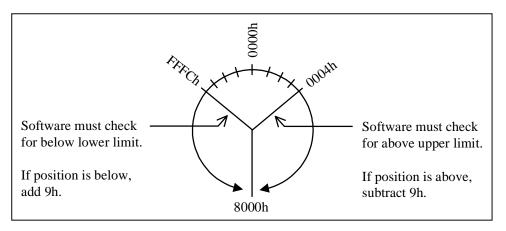

Finally, the position value must be manually rolled over in order to obtain the desired number sequence. Figure 3 illustrates the adjustment for a 9-count-per-revolution encoder.

Figure 3. Software rollover adjustment for a 9 count/revolution encoder

The following code illustrates this method using GP Timer 3 to hold the counts from a 9-count-per-revolution encoder.

| Example 2. Code Listing #2             |                                                                                  |                                                                                                |                                                                                                                                                                                                                                                                                                             |  |  |

|----------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| T3CNT<br>CAP3FIFO<br>EVIFRC<br>EVIMRC  | .set<br>.set<br>.set<br>.set                                                     | 7409h<br>7425h<br>7431h<br>742Eh                                                               |                                                                                                                                                                                                                                                                                                             |  |  |

| temp<br>old_count                      | .bss<br>.set<br>.set                                                             | position,<br>position+<br>position+                                                            | 1                                                                                                                                                                                                                                                                                                           |  |  |

| count_rev<br>upper_lim<br>lower_lim    | .data<br>.int<br>.int<br>.int                                                    | 4 ;                                                                                            | encoder counts per revolution<br>rupper limit of desired sequence<br>lower limit of desired sequence                                                                                                                                                                                                        |  |  |

| ************************************** |                                                                                  |                                                                                                |                                                                                                                                                                                                                                                                                                             |  |  |

| ;position = posit<br>;check for rollo  | CLRC<br>SETC<br>LDP<br>LACC<br>LDP<br>SACL<br>SUB<br>ADD<br>SACL<br>LACC<br>SACL | OVM<br>SXM<br>#232<br>T3CNT<br>#position<br>temp<br>old_count<br>position<br>temp<br>old_count | <pre>;overflow mode off<br/>;use signed math<br/>;data page set to event manager<br/>;ACC = new_count<br/>;set data page<br/>;temporarily store new count<br/>;subtract old count<br/>;add previous position<br/>;store new position to memory<br/>;ACC = new_count<br/>;store new_count as old_count</pre> |  |  |

| GHECK LOL LOLLO                        | LACC                                                                             | position                                                                                       | ;ACC = new position                                                                                                                                                                                                                                                                                         |  |  |

#### Example 2. Code Listing #2

| under:<br>over:                 | LDP<br>SUB<br>BCND<br>LDP<br>LACC<br>LDP<br>SUB<br>BCND<br>ADD<br>LDP<br>SACL<br>B<br>ADD<br>SUB<br>LDP<br>SACL | <pre>#upper_lim<br/>upper_lim<br/>over, GT<br/>#position<br/>position<br/>#lower_lim<br/>lower_lim<br/>done, GEQ<br/>lower_lim<br/>count_rev<br/>#position<br/>done<br/>upper_lim<br/>count_rev<br/>#position<br/>position<br/>position</pre> | <pre>;set data page<br/>;subtract upper limit<br/>;branch if above upper limit<br/>;set data page<br/>;ACC = new position<br/>;set data page<br/>;subtract lower limit<br/>;done if above lower limit<br/>;ACC = new position<br/>;add count_rev<br/>;set data page<br/>;store adjusted position<br/>;done<br/>;ACC = new position<br/>;done<br/>;ACC = new position<br/>;subtract count_rev<br/>;set data page<br/>;store adjusted position</pre> |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| done:                           |                                                                                                                 | -                                                                                                                                                                                                                                             | ;main code continues                                                                                                                                                                                                                                                                                                                                                                                                                               |

| * * * * * * * * * * * * * * * * | * * * * * * * * *                                                                                               | * * * * * * * * * * * * * * * *                                                                                                                                                                                                               | * * * *                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 |                                                                                                                 | ot Service Rout                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *****                           |                                                                                                                 | * * * * * * * * * * * * * * * *                                                                                                                                                                                                               | * * * * *                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| STATUS                          | .usect                                                                                                          |                                                                                                                                                                                                                                               | must be located on DP 0                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | .bss CO                                                                                                         | NTEXT, 2, 1                                                                                                                                                                                                                                   | ;context saving area                                                                                                                                                                                                                                                                                                                                                                                                                               |

| cap3int:                        | .text<br>SST<br>SST<br>LDP<br>SACH<br>SACL<br>LDP<br>LACC<br>LDP<br>SACL<br>SPLK<br>LACC                        | <pre>#0, STATUS #1, STATUS+1 #CONTEXT CONTEXT CONTEXT+1 #232 CAP3FIF0 #position old_count #0, position EVIMRC</pre>                                                                                                                           | <pre>;save ST0<br/>;save ST1<br/>;set data page<br/>;save high accumulator<br/>;save low accumulator<br/>;DP set to event manager<br/>;ACC = captured value<br/>;set data page<br/>;init old_count with<br/>; captured value<br/>;zero the position<br/>;ACC loaded with</pre>                                                                                                                                                                     |

|                                 | AND<br>SACL<br>SPLK<br>LDP<br>LACL<br>ADD<br>LDP<br>LST<br>LST<br>CLRC<br>RET                                   | <pre>#1011b EVIMRC #0100b, EVIFRO #CONTEXT CONTEXT+1 CONTEXT,16 #0 #1, STATUS+1 #0, STATUS INTM</pre>                                                                                                                                         | ; EV Mask Register C<br>;mask off CAP3INT bit<br>;disable CAP3INT<br>C;clear CAP3INT flag<br>;set data page<br>;restore low accumulator<br>;restore high accumulator<br>;set data page<br>;restore ST1<br>;restore ST0<br>;re-enable global interrupts<br>;return                                                                                                                                                                                  |

Absolute position referencing has been accomplished through proper initialization of position and old\_count. The above code uses the encoder index signal in conjunction with Capture #3 to perform the initialization in the Capture #3 interrupt service routine. During the interrupt service routine, position is set to zero and old\_count is initialized with the captured count value. The Capture #3 interrupt is then disabled prior to returning to the main code so that encoder initialization is only performed once.

The code is easily modified for other encoder resolutions and for position discrimination over multiple revolutions by changing the assigned values for count\_rev, upper\_lim, and lower\_lim. The assigned values must satisfy (N\*count\_rev - 1) = (upper\_lim - lower\_lim), where N equals the number of revolutions. For example, to obtain position over two complete revolutions of the example 9 count/revolution encoder, one could set upper\_lim to 8 and lower\_lim to -9. Alternately, one could set upper\_lim to 9 and lower\_lim to -8.

Note that position must never cross the boundary at 8000h in either direction. Normally, this is not a problem except in the uncommon situation where upper\_lim and lower\_lim begin to approach 8000h, or when the sample rate is unusually low so that new\_count minus old\_count becomes large. The code would need to be modified if crossing this boundary becomes a possibility.

#### **Obtaining Signed Position:**

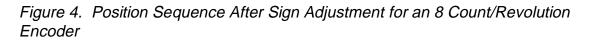

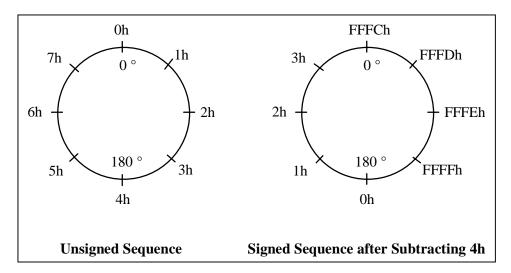

The desired number sequence shown in Figure 1 is an unsigned sequence representing 0 to 360 degrees, as opposed to a signed sequence representing -180 to +180 degrees. As illustrated in this paper, Methods 1 and 2 always produce such an unsigned sequence, while Method 3 can directly produce either a signed or an unsigned sequence depending on the values assigned to upper\_lim and lower\_lim. If a signed sequence is desired when using Methods 1 or 2, first obtain the unsigned sequence as previously shown. A 2's compliment sequence that is properly signextended to 16 bits can then be obtained by subtracting half the number of counts per revolution from the unsigned position. For example, with a 1024 count/revolution encoder subtract 512 = 200h. With a 1000 count/revolution encoder subtract 500 = 1F4h. Figure 4 depicts a subtraction of 4 with an 8-count-per-revolution encoder. Note that the absolute position is now referenced to a position 180 degrees away from the original reference position.

When discriminating position over multiple revolutions, the subtracted value should equal half the total number of counts for the multiple revolutions. For example, when discriminating four revolutions with an 8-count-per-revolution encoder, the subtracted value should be 16 = 10h.

**i**j