# Horloge à LED

Diana GRATADE - Q1

Benjamin TUILARD - P2

Promotion 2011/2013

#### **Enseignants:**

Dominique BESSE Charles GLIKSOHN Thierry LEQUEU Patrick PAPAZIAN

#### Sommaire

#### 1. Présentation du sujet

- 1.1 Fonctionnement global

- 1.2 Synoptiques du projet

- 1.3 Etude du cahier des charges

- 1.4 Planning réel et prévisionnel

#### 2. Description technique de l'horloge

- 2.1 Le bus I2C

- 2.2 L'ATmega

- 2.3 Le RTC

- 2.4 La CPLD

#### 3. Mise en œuvre et réalisation de l'horloge

- 3.1 La partie électronique: réalisation des typons

- 3.2 La partie informatique: programmation

#### 4. Bilan du projet

Principe de fonctionnement de global

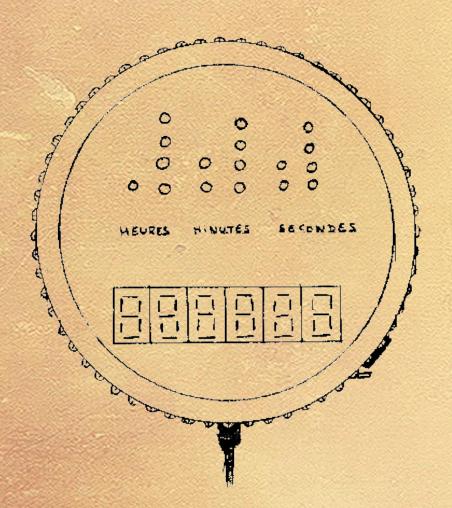

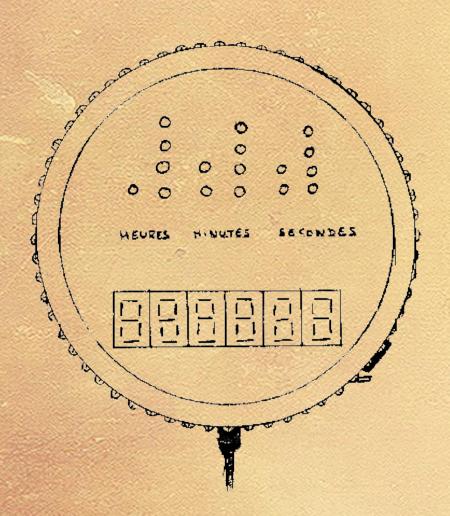

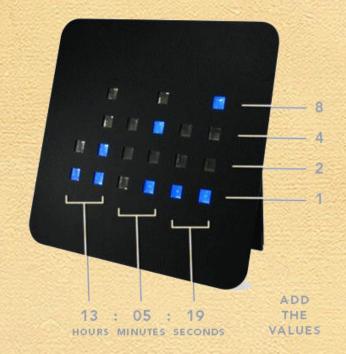

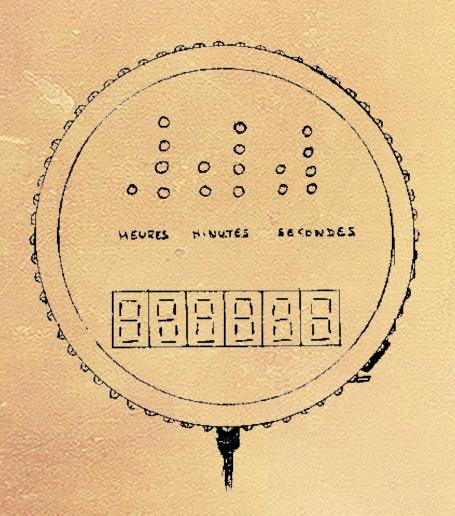

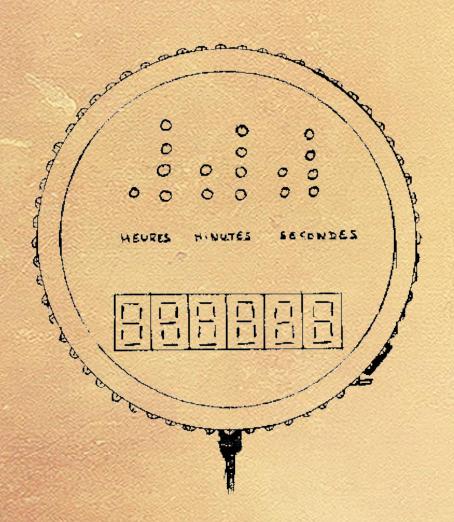

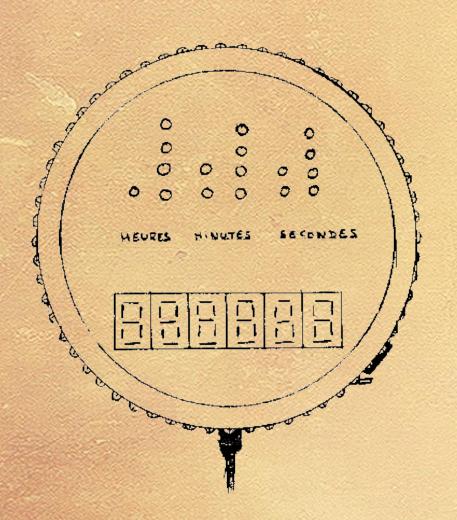

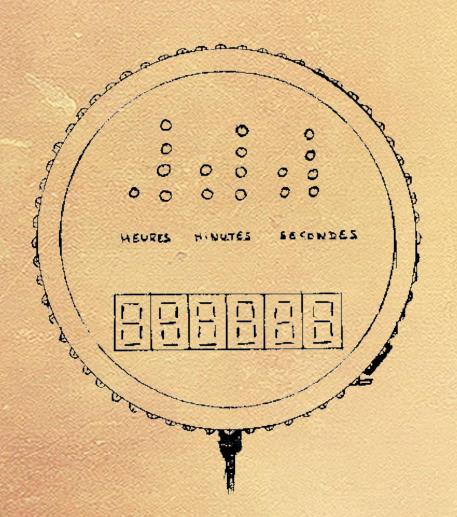

Croquis de l'horloge à réaliser

3 modes d'affichages:

**Traditionnel**

Exemple d'affichage traditionnel à base de LEDs

Principe de fonctionnement de global

3 modes d'affichages:

Traditionnel Binaire

Exemple d'horloge binaire

Principe de fonctionnement de global

3 modes d'affichages:

**Traditionnel**

**Binaire**

**Digital**

Principe de fonctionnement de global

3 modes d'affichages:

**Traditionnel**

**Binaire**

**Digital**

Alimentation générale 0/+5V

Principe de fonctionnement de global

3 modes d'affichages:

**Traditionnel**

**Binaire**

**Digital**

Alimentation générale 0/+5V

Heure réglable

Principe de fonctionnement de global

3 modes d'affichages:

**Traditionnel**

**Binaire**

**Digital**

Alimentation générale 0/+5V

Heure réglable

Sauvegarde de l'heure en mémoire en cas de coupure d'alimentation

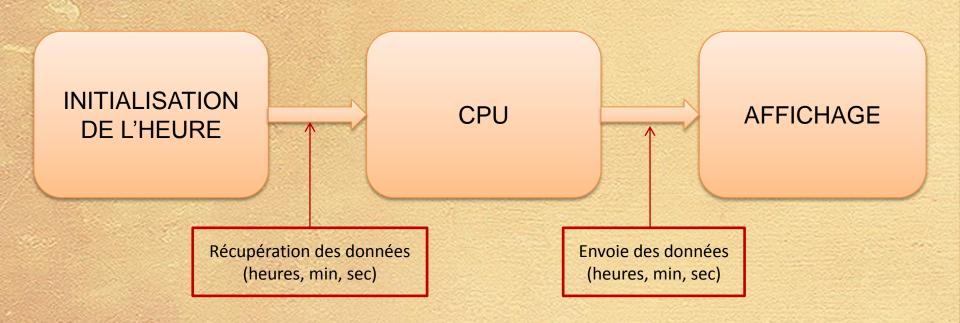

Synoptique du projet - Niveau 1

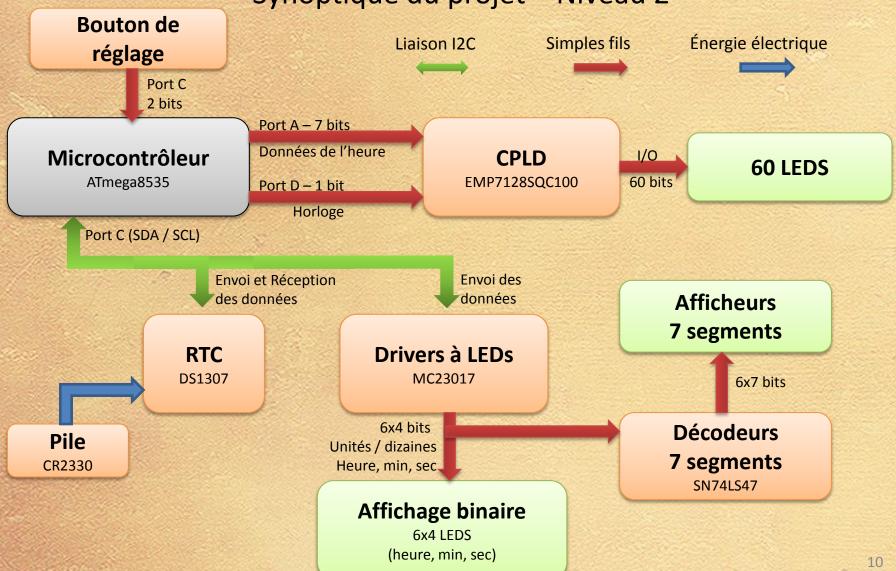

Synoptique du projet - Niveau 2

#### Étude du cahier des charges

#### Division du travail en 2 parties :

Benjamin

Étude du RTC et des drivers à LEDs

#### Réalisations:

- Carte de l'ATmega8535

- Carte drivers à LEDs

- Carte d'alimentation

Programmation de l'Atmega8535

**Communication** Bus I2C

Diana

Étude du bus 12C

#### Réalisations:

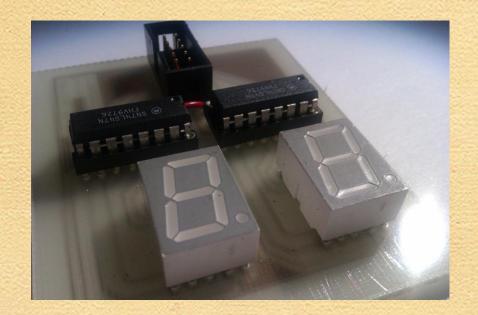

- Carte de l'affichage digital

- Carte de la CPLD

- Carte de l'affichage traditionnel

**Programmation** de la CPLD

Communication ATmega8535/CPLD

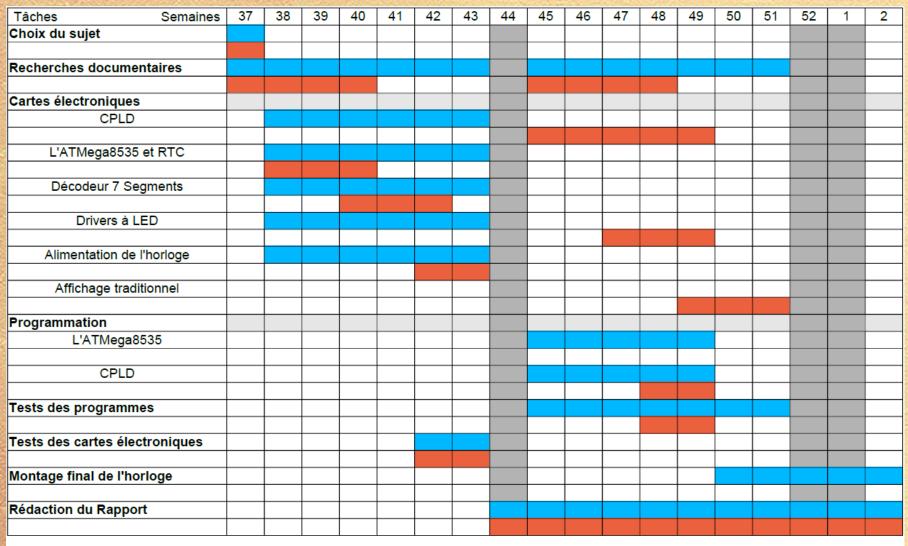

#### Planning réel et prévisionnel

Planning réel

Planning prévisionnel

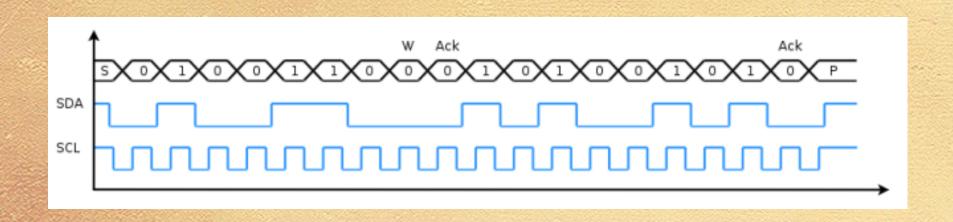

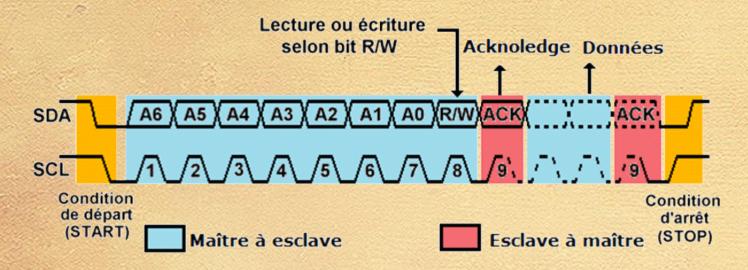

Le Bus I2C: Inter Integrate Circuit

Logo du Bus I2C

3 fils permettant d'échanger des informations:

**SDA** : signal de données

**SCL**: signal d'horloge

Masse : référence électrique

Le Bus I2C: Inter Integrate Circuit

Logo du Bus I2C

3 fils permettant d'échanger des informations:

SDA: signal de données

SCL: signal d'horloge

Masse: référence électrique

Communication par adressage entre maître/esclaves

L'ATmega: le microcontrôleur

#### Diverse fonctions intégrées:

- Horloge interne

- Convertisseur

- MLI

- etc...

| (XCK/T0) PB0 □       | 1  | 40 | PA0 (ADC0)    |

|----------------------|----|----|---------------|

| (T1) PB1 □           | 2  | 39 | PA1 (ADC1)    |

| (INT2/AIN0) PB2      | 3  | 38 | □ PA2 (ADC2)  |

| (OC0/AIN1) PB3       | 4  | 37 | □ PA3 (ADC3)  |

| (SS) PB4 □           | 5  | 36 | □ PA4 (ADC4)  |

| (MOSI) PB5 □         | 6  | 35 | □ PA5 (ADC5)  |

| (MISO) PB6 □         | 7  | 34 | PA6 (ADC6)    |

| (SCK) PB7 □          | 8  | 33 | □ PA7 (ADC7)  |

| RESET [              | 9  | 32 | □ AREF        |

| VCC 🗆                | 10 | 31 | GND           |

| GND □                | 11 | 30 | □ AVCC        |

| XTAL2                | 12 | 29 | □ PC7 (TOSC2) |

| XTAL1                | 13 | 28 | □ PC6 (TOSC1) |

| (RXD) PD0 □          | 14 | 27 | □ PC5         |

| (TXD) PD1 $\Box$     | 15 | 26 | □ PC4         |

| (INT0) PD2 □         | 16 | 25 | □ PC3         |

| (INT1) PD3 □         | 17 | 24 | □ PC2         |

| (OC1B) PD4 $\square$ | 18 | 23 | □ PC1 (SDA)   |

| (OC1A) PD5 $\square$ | 19 | 22 | PC0 (SCL)     |

| (ICP1) PD6 □         | 20 | 21 | □ PD7 (OC2)   |

|                      |    |    |               |

Programmé avec « Code Vision AVR »

Le RTC: Real Time Clock

Horloge à temps réel

**Avantages**

Inconvénients

- **RTC DS1307**

- Continuité de fonctionnement

- Fournit l'heure et la date

- Prend en compte les années bissextiles

- Communication en I2C

#### 2 phases de fonctionnement : initialisation et envoi des données

| ADDRESS | BIT 7   | BIT 6         | BIT 5     | BIT 4       | BIT 3   | BIT 2 | BIT 1   | BIT 0          | FUNCTION      | RANGE   |

|---------|---------|---------------|-----------|-------------|---------|-------|---------|----------------|---------------|---------|

| 00h     | CH      | CH 10 Seconds |           | Seconds     |         |       | Seconds | 00–59          |               |         |

| 01h     | 0       | 10 Minutes    |           |             | Minutes |       |         | Minutes        | 00–59         |         |

| 02h 0   | 12      | 10<br>Hour    | 10        | Hours       |         |       | Hours   | 1–12<br>+AM/PM |               |         |

|         | O       | 24            | PM/<br>AM | Hour        | riours  |       |         | riours         | 00–23         |         |

| 03h     | 0       | 0             | 0         | 0           | 0 DAY   |       |         |                | Day           | 01–07   |

| 04h     | 0       | 0             | 0 10 Date |             |         | Date  |         |                | Date          | 01–31   |

| 05h     | 0       | 0             | 0         | 10<br>Month | Month   |       |         |                | Month         | 01–12   |

| 06h     | 10 Year |               |           | Year        |         |       | Year    | 00–99          |               |         |

| 07h     | OUT     | 0             | 0         | SQWE        | 0       | 0     | RS1     | RS0            | Control       | _       |

| 08h-3Fh |         |               |           |             |         |       |         |                | RAM<br>56 x 8 | 00h–FFh |

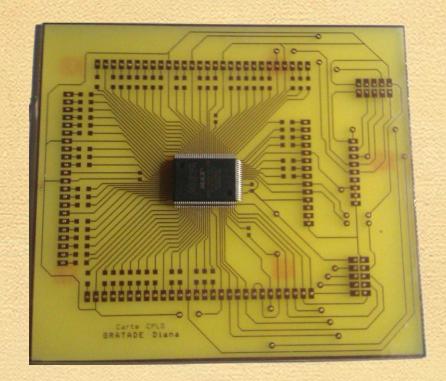

Le CPLD: Complex Programmable Logic Device

Composant logique programmable

Non compatible avec le bus I2C

Communication avec l'ATmega via:

- 6 bits pour la réception des données

- 1 bit de mode pour identifier les données

Simulation du fonctionnement de registre à décalages

Programmée à l'aide du logiciel « Quartus »

La partie électronique: réalisation des typons

Réalisation de 6 cartes électroniques différentes

- Carte de l'alimentation

La partie électronique: réalisation des typons

- Carte de l'alimentation

- Carte de l' ATmega

La partie électronique: réalisation des typons

- Carte de l'alimentation

- Carte de l' ATmega

- Carte de la CPLD

La partie électronique: réalisation des typons

- Carte de l'alimentation

- Carte de l' ATmega

- Carte de la CPLD

- Carte de l'affichage traditionnel

La partie électronique: réalisation des typons

- Carte de l'alimentation

- Carte de l' ATmega

- Carte de la CPLD

- Carte de l'affichage traditionnel

- Carte des drivers à LEDs

La partie électronique: réalisation des typons

- Carte de l'alimentation

- Carte de l' ATmega

- Carte de la CPLD

- Carte de l'affichage traditionnel

- Carte des drivers à LEDs

- Carte des afficheurs 7-segments

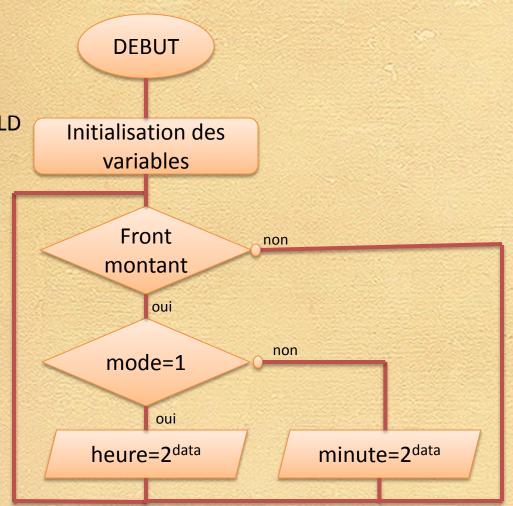

La partie informatique: programmation

Ordinogramme du programme de la CPLD

Initialisation des variables

Déclaration des entrées/sorties

Front montant de l'horloge

### Bilan du projet

Création d'une horloge dotée de 3 modes d'affichages

Réalisation de plusieurs cartes électroniques et programmation de la CPLD

Mise en application de nos connaissances personnelles

Développer les facultés de gestion, d'analyse et d'adaptation lors d'un projet

Projet pas entièrement abouti mais pouvant être repris au semestre 4

Amélioration de l'horloge par des diodes RGB et par l'affichage de la date