## Announcement

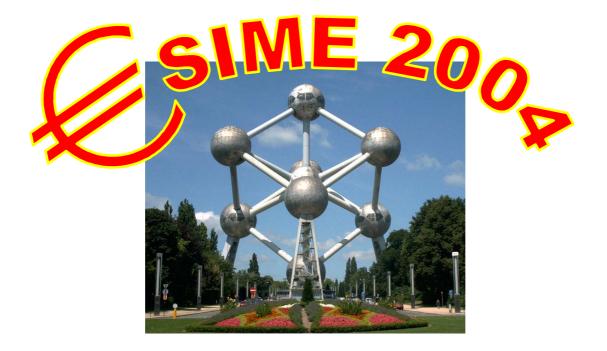

5th international conference on thermal & mechanical simulation and experiments in micro-electronics and micro-systems

## www.eurosime.com

May 9 - May 12, 2004

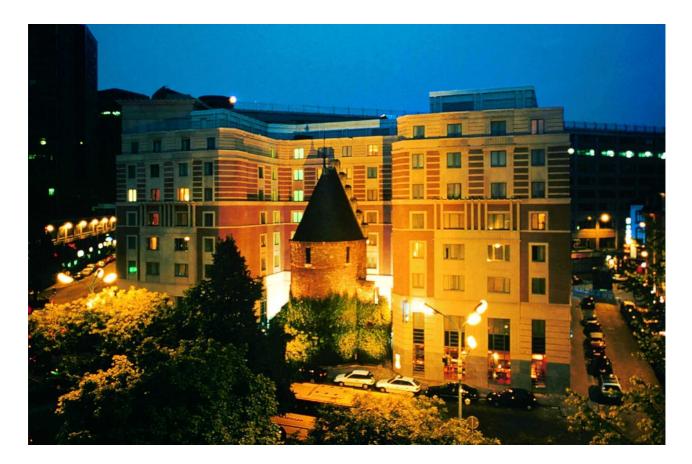

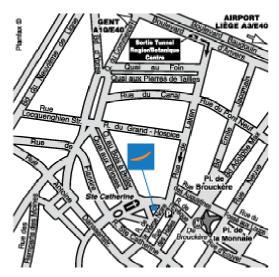

Novotel Tour Noire Brussels, Belgium

**EuroSimE 2004** provides ... .....7 courses given by professionals .....90 papers in 18 oral and 3 poster sessions .....exhibition and exhibitor presentations

Local organiser: Bart.Vandevelde@imec.be, Marion.Hegemann@imec.be (tel.: +32 16 281 849).

## Conference overview

| Sunday        | May 9, 2004 Short courses                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------|

| 8.30 - 9.00   | Registration for short courses (IMEC-Leuven)                                                                         |

| 9.00 - 12.30  | C1: cancelled                                                                                                        |

|               | C2: Application of static and dynamic compact thermal models for the thermal analysis of electronic parts (M. Sabry) |

|               | C4: Advanced optimization methods for design and qualification of microelectronics (N. Tzannetakis, G.Q. Zhang)      |

|               | C6: Fundamentals of board-level assembly and solder joint reliability (R. Lee)                                       |

|               | C8: Wafer level packaging technologies (E. Beyne)                                                                    |

| 12.30 - 14.00 | Lunch                                                                                                                |

| 14.00 - 17.30 | C1: cancelled                                                                                                        |

|               | C3: Heat sink design and analysis for microelectronic equipment (P. Rodgers, V. Eveloy)                              |

|               | C5: Lead-free Solder Joints: Reliability Trends and Material Properties (J-P. Clech)                                 |

|               | C7: Microvias and high density interconnects for advanced packaging (R. Lee)                                         |

| 18.00         | Bus to Novotel Brussels (conference location)                                                                        |

SIME 200

| Monday        | May 10, 2004 Conference program, day 1                        |

|---------------|---------------------------------------------------------------|

| 7.30 - 8.30   | Registration                                                  |

| 8.30 - 10.40  | Session 1: Industrial Trends                                  |

| 10.40 - 11.10 | Coffee break                                                  |

| 11.10 - 12.40 | Session 2: Technology Developments                            |

| 12.40 - 14.20 | Lunch                                                         |

| 14.20 - 15.50 | Session 3: Virtual Thermal Mechanical Prototyping             |

| 14.20 - 15.50 | Session 4: Thermal Mechanical Behaviour on Wafer Level        |

| 14.20 - 15.50 | Session 5: Dynamic Compact Thermal and Electro-Thermal Models |

| 15.50 - 16.30 | Coffee break                                                  |

| 16.30 - 18.00 | Session 6: Experimental and Numerical Interaction             |

| 16.30 - 18.00 | Session 7: Modelling and Designing of Advanced Packaging      |

| 16.30 - 18.00 | Session 8: Thermal Behaviour Modelling and Characterization   |

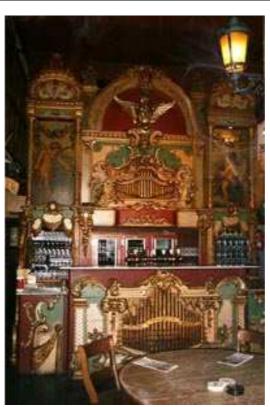

| 19.30 - 23.00 | Gala dinner in "Roy d'Espagne"                                |

| Tuesday       | May 11, 2004 Conference program, day 2                            |

|---------------|-------------------------------------------------------------------|

| 8.30 - 10.20  | Session 9: Advanced Numerical Simulation Methodologies            |

| 8.30 - 10.20  | Session 10: Small Scale Thermal and Fluid Aspects in Microsystems |

| 10.20 - 10.40 | Coffee break                                                      |

| 10.40 - 11.30 | Poster session 11, 12, 13.                                        |

| 11.30 - 12.40 | Session 14: Modelling of MEMS and Optical Devices                 |

| 11.30 - 12.40 | Session 15: Simulation-Based Thermal Design Strategies            |

| 12.40 - 14.10 | Lunch                                                             |

| 14.20 - 16.10 | Session 16: Solder Reliability Behaviour                          |

| 14.20 - 16.10 | Session 17: CFD and FE Modelling of Thermal Performance           |

| 16.10 - 16.30 | Coffee break                                                      |

| 16.30 - 18.00 | Special exhibitor session                                         |

| 18.00 - 19.30 | Cocktail party                                                    |

| Wednesday     | May 12, 2004 Conference program, day 3                                          |  |

|---------------|---------------------------------------------------------------------------------|--|

| 8.30 - 10.00  | Session 18: Micro- to Macro-Scale Thermal Design Challenges in Microelectronics |  |

| 10.00 - 10.40 | Coffee break                                                                    |  |

| 10.40 - 12.30 | Session 19: Solder Fatigue                                                      |  |

| 10.40 - 12.30 | Session 20: Characterization and Modelling of Polymer behaviour                 |  |

| 12.30 - 14.00 | Lunch                                                                           |  |

| 14.00 - 16.00 | Session 21: New Developments in Microelectronics Reliability                    |  |

| 16.00         | End of the conference                                                           |  |

## Sunday May 9, 2004: Short courses

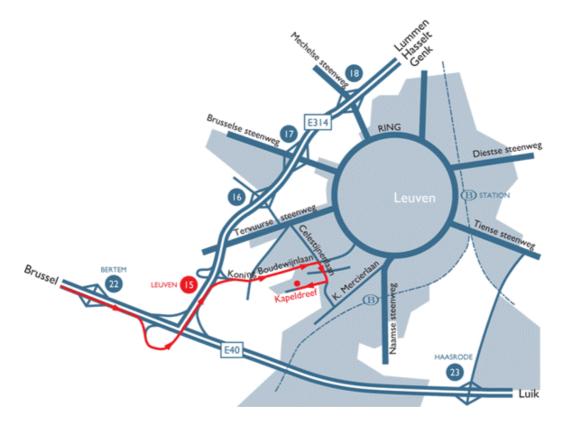

## Place and date : Leuven – (IMEC)

| 8.30 - 9.00   | Registration for short courses (IMEC-Leuven)                                                                         |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 9.00 - 12.30  | C2: Application of static and dynamic compact thermal models for the thermal analysis of electronic parts (M. Sabry) |  |  |

|               | C4: Advanced optimisation methods for design and qualification of microelectronics (N. Tzannetakis, G.Q. Zhang)      |  |  |

|               | C6: Fundamentals of board-level assembly and solder joint reliability (R. Lee)                                       |  |  |

|               | C8: Wafer level packaging technologies (E. Beyne)                                                                    |  |  |

| 12.30 - 14.00 | Lunch                                                                                                                |  |  |

| 14.00 - 17.30 | C3: Heat sink design and analysis for microelectronic equipment ( <b>P. Rodgers</b> , <b>V. Eveloy</b> )             |  |  |

|               | C5: Lead-free Solder Joints: Reliability Trends and Material Properties (J-P. Clech)                                 |  |  |

|               | C7: Microvias and high density interconnects for advanced packaging (R. Lee)                                         |  |  |

| 18.00         | Bus to Novotel Brussels (conference location)                                                                        |  |  |

## Attention!!! The location of the courses is different from the location of the conference.

#### Course description:

| Course 1: | Cancelled |  |  |  |  |

|-----------|-----------|--|--|--|--|

|-----------|-----------|--|--|--|--|

| Course 2:    | Application of static and dynamic compact thermal models for the thermal analysis of electronic parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instructor   | Mohamed-Nabil Sabry, French University, Egypt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Introduction | The impact of thermal effects on both reliability and performance of electronic systems is no longer to be proved.<br>Static and dynamic thermal effects in electronic circuits manifest themselves at all levels from device to system, with<br>high impact on both reliability and performance of electronic systems, especially as the device feature size shrinks to<br>the nano-scale. Progress in electronic systems has always been marked by a trend for smaller devices and hence larger<br>systems in terms of number of devices. Breaking the barriers at both ends, small and large, is continuously creating<br>new challenges for EDA industry. In fact, for small sizes, the electronic behaviour will be more affected by other<br>physical phenomena such as thermal, electromagnetic and mechanical including quantum effects. This constitutes the<br>first challenge. On the other hand, miniaturization enables us to construct systems containing millions, or perhaps<br>billions, of different elements. Hence, modelling, simulating and moreover optimising these systems, is another<br>challenge. It is evident that analysing a thermal problem in its full details, involving fluid dynamics, heat transfer by all<br>modes (conduction, convection and radiation) including non-linear effects together with all the electronic details of the<br>system is simply a fiction. Yet, electronic and thermal problems interfere at all levels, and we need to predict system<br>performance and reliability before fabrication. Hence, new design methodologies have to be adopted based on top -<br>down design approach. This is a "divide and conquer" approach, heavily relying on hierarchical sets of compact<br>models at different levels of abstraction. |  |  |

|              | to the dynamic case. The wealth of knowledge accumulated has largely deserved a structured presentation in order to correctly grasp underlying physics as well as adequate methodologies to handle different problems according to their inherent nature as well as design needs and constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Objectives   | The course aims at giving attendees a rational and structured understanding of the nature of both compact models as well as physical problems they are intended to address, whether in static or dynamic regimes, in order to adequately build and use these compact models for the design and analysis of electro-thermal problems arising in electronic systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Course<br>Outline       | <ol> <li>Introduction         <ul> <li>When and why should we care about electro-thermal effects</li> <li>Why should we use compact models</li> <li>Place of compact models in simulation and design flow</li> </ul> </li> <li>Properties of a compact model         <ul> <li>General forms for static and dynamic models</li> <li>Constraints that must be satisfied by compact models, validity checks</li> <li>Precision of a compact model</li> </ul> </li> <li>When should we use a dynamic compact model?         <ul> <li>Slow dynamics</li> <li>Fast dynamics</li> <li>Fast dynamics</li> <li>Structural assembly approach</li> <li>Integral approach</li> <li>The structure function</li> <li>Modal approach</li> </ul> </li> <li>Special problems</li> <li>Nonlinear problems, Radiation         <ul> <li>Convection</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Who should attend?      | The course addresses the needs of engineers, scientists as well as technical strategic decision makers, involved in thermal management of electronic systems. Although the course presents most recent advances in the field of static and dynamic compact models with sufficient details to let this knowledge be operational in concrete applications, it does not assume prior knowledge of these issues and hence is of interest for both experts and new actors in this area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| About the<br>instructor | Prof. Mohamed-Nabil Sabry is the dean of engineering faculty in the French University in Egypt. He holds a Doctorat es Sciences Degree from the National Polytechnic Institute in Grenoble, France 1984, about modeling and simulation of 3D convective problems and has been involved since then in thermal and electro-thermal issues at different levels both in academic and industrial context. He was formerly with Mentor Graphics where he was the engineering manager of analog simulation activities worldwide, as well as the French Nuclear Research Center. He also worked with different universities in France (INP-Grenoble) and in Egypt (Mansoura U., American U. and finally the French U.). For his publications on compact models, he was awarded the Harvey Rosten award of excellence in 2002. He is also member of the program committee of THERMINIC, a panel member in many international conferences (THERMINIC, VLSI Test Symposium) and a reviewer in many international scientific journals dealing with this subject (IEEE/CPT, IEEE/Electron Device letters, Microelectronics Journal, ASME/Journal of Electronic Packaging). His published works cover the whole spectrum of electro-thermal analysis from transistor level to system level. |  |

| Course 3:    | Heat sink design and analysis for microelectronic equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instructor   | Peter Rodgers, CALCE Electronic Products and Systems Center, University of Maryland, USA Valérie Eveloy, Electronics Thermal Management Ltd., Ireland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Introduction | Heat sinks are the most common, cost-effective hardware employed for the thermal management of microelectronic equipment, with applications spanning from microchannel cooling to component- and circuit board thermal control. Heat sinks function by extending the surface area of heat dissipating surfaces through the use of fins. Their design and analysis is one of the most extensive research areas in electronics cooling. Ever-rising electronic component power dissipation, combined with both the demand for more compact and lighter equipment, and manufacturing constraints, place increasing challenges on the optimisation of heat sink thermal performance today. This is compounded by shortening product design cycle times, which heighten the requirement for innovative thermal design methods enabling accurate heat sink designs to be generated and quickly assessed. An efficient thermal design process involves the use of analytical and semi-empirical calculations to establish an initial heat sink design, which is refined by numerical analysis to account for the impact of the application environment on thermal performance. The effectiveness of the heat sink design ultimately needs to be verified by experimentation. The course provides an overview of the state-of-the-art and general trends in heat sink design. Apart from convective and radiative heat transfer optimisation, the course addresses key issues in advancing heat sink thermal performance, including contact thermal resistance, integration of heat spreading technologies and entropy minimisation. Practical case studies dealing with heat sink design optimisation are presented. |  |

| Objectives   | This course provides a comprehensive treatment of the design and analysis of heat sinks. It combines theoretical and practical information to successfully design or select cost-effective heat sinks for microelectronic equipment. The attendee will gain an appreciation of both the fundamental performance limits of heat sinks, and current state-of-the-art in heat sink technology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Course<br>Outline | <ol> <li>Introduction         <ul> <li>Fundamentals of heat transfer: conductive, convective and radiative heat transfer processes</li> <li>Thermal analysis and design process: Application of analytical, experimental and numerical analyses, overview of the latest commercial thermal design software packages</li> <li>Heat dissipation trends in electronic systems: heat transfer chain, limits of air-cooling: passive versus active</li> </ul> </li> <li>Evolution of Heat Sink Design and Analysis         <ul> <li>Analytical analysis: Fin efficiency, Radiative heat transfer models</li> <li>Experimentation: derivation of correlations for the convective heat transfer coefficient as a function of heat sink geometry and convective environment; friction factor correlations</li> <li>Numerical analysis: Investigation of thermofluid phenomena: Use of Computational Fluid Dynamics (CFD) methods to predict heat sink performance in application environment</li> <li>Heat sink design optimisation                 <ul></ul></li></ul></li></ol> |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Comme             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ouume             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | Environmental and physical conditions; Initial feasibility study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | Heat sink optimisation: Convective and radiative performance; Conductive performance (Fin efficiency, heat spreading: heat pipes, vapour chambers, improved thermal conductivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | materials), design for manufacturability, least-energy optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | 5. Current Design and Analysis Methods for Air-Cooled Heat Sinks (Cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | • Heat sink attachment: contact thermal resistance and interface materials, properties of interface materials;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   | Types of interface materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | Airflow management     For particular                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | Fan performance<br>Fan/blower/impeller selection; Assessment of vendor specified fan curve performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | Change in fan curve characteristics due to application environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | Effect of grille and filter open area on system impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | Compact modelling of heat sink thermofluid characteristics for system-level numerical analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   | 6. Case studies: heat sink design and application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   | Microprocessor cooling     Take any maintain a biast wait as a line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | Telecommunication cabinet unit cooling     Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Who should        | The course will benefit engineers, managers and scientists involved in the thermal management or reliability of electronic systems. It is aimed at participants with varying expertise levels in thermal management, from novice to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| attend?           | advanced.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| About the<br>instructor | <ul> <li>Dr. Peter Rodgers is an Assistant Research Professor at the University of Maryland, College Park, where he supports the thermofluid research of the CALCE Electronic Products and Systems Center. He holds a Ph.D. degree in mechanical engineering from the University of Limerick, Ireland and has extensive experience of electronic equipment thermal design and characterisation. He was formerly with Electronics Thermal Management Ltd., Ireland, and the Nokia Research Center, Finland, where he consulted on electronics cooling. He is recipient of the 1999 Harvey Rosten Award for Excellence, awarded for his publications on the application of CFD analysis to electronics thermal design. Other research interests include the design of high-performance heat sinks, and the development of advanced experimental techniques to characterise thermofluid phenomena in electronic systems. He is a participant in the JSME Project, "Design and Manufacture of High-Performance Heat Sinks for Microelectronic Equipment". He is a member of several international conference program committees and has authored or co-authored approximately forty conference and journal publications on a broad range of topics related to electronics cooling. He has been an invited lecturer, track- and session chair and panelist at international conferences.</li> <li>Dr. Valérie Eveloy is with Electronics Thermal Management Ltd., a research and consulting firm specialized in electronics cooling. She has been involved in electronics cooling for nine years, and was previously a Research Engineer with the Nokia Research Center, Finland, where her activities focused on the thermal management of telecommunication products and the selection of RF IC packaging solutions. She has authored or co-authored over twenty five conference and journal publications, holds an M.Sc. degree in physical engineering from the National Institute of Applied Science (INSA), France, and a Ph.D. degree in mechanical engineering from Dublin City University, Ireland.</li> </ul> |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Course 4:                 | Advanced optimisation methods for design and qualification of microelectronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|