# 15<sup>th</sup> EUROPEAN SYMPOSIUM RELIABILITY OF ELECTRON DEVICES, FAILURE PHYSICS AND ANALYSIS

Zürich — Switzerland 4 – 8 October 2004

with the technical co-sponsorship of:

IEEE - Electron Devices Society - Reliability Society

DEVICES

**Reliability Society**

with the support of:

ETH Zürich

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

in conjunction with:

EOBT (Electron and Optical Beam Testing)

organised by:

IIS Integrated Systems Laboratory ETH Zürich

| 8 30 Tut 4 (D)                                |

|-----------------------------------------------|

| 30 Tut 4                                      |

|                                               |

| 11 0 Opening (A)                              |

| 2 20 Keynote Speech (A)                       |

|                                               |

|                                               |

| Lunch                                         |

| 0                                             |

| Asbl (A)                                      |

| 14 40 Asbl 14 30 Comp (B) 15 S Asbl 15 S Comp |

| Asbl 15 30                                    |

| Asbl 15                                       |

| 16 50 Ach   16 50 Comp                        |

| 15 Asbi                                       |

| 7 40                                          |

|                                               |

| ) Rec                                         |

| 9 50 Session Party                            |

|                                               |

|                                               |

|                                               |

| Auditorium Maximum                            |

| D / .2                                        |

| D 1.2<br>D 7.2                                |

# **ESREF Steering Committee**

| X. Aymerich<br>L. J. Balk<br>J. Bisschop | Univ. of Barcelona<br>Univ. of Wuppertal<br>Philips | E<br>D<br>NL |

|------------------------------------------|-----------------------------------------------------|--------------|

| M. Ciappa                                | ETH Zurich                                          | CH           |

| Y. Danto                                 | Univ. of Bordeaux                                   | F            |

| F. Fantini                               | Univ. of Modena                                     | 1            |

| J. P. Fortea                             | CNES                                                | F            |

| W. Gerling                               | Infineon                                            | D            |

| C. Lindsay                               | Marconi                                             | UK           |

| V. Loll                                  | Nokia                                               | DK           |

| L. Lonzi                                 | STMicroelectronics                                  | 1            |

| G. Groesenecken                          | IMEC                                                | В            |

| J. Moeltoft                              | Technical Univ. of Denmark                          | DK           |

| A. J. Mouthaan                           | Univ. of Twente                                     | NL           |

| N. Stojadinovic                          | Univ. of Nis                                        | Υ            |

| R. Thomas                                | Technology Experts Network                          | USA          |

| W. Wondrak                               | Daimler Chrysler                                    | D            |

# **Program Committee**

| Wolfgang Fichtner | General Chair            |

|-------------------|--------------------------|

| Mauro Ciappa      | Technical Program Chair  |

| Dölf Aemmer       | Local Organization Chair |

| Christine Haller  | Conference Secretary     |

| Bruno Fischer     | Exhibition Officer       |

| Anja Böhm         | WEB officer              |

## **Technical Program Committee of ESREF 2004**

Chair Mauro Ciappa ETH Zürich CH

#### Sub-Com Circuits, Systems, and Assembly Reliability

Marcantonio Catelani Univ. Firenze ı Yves Danto Univ. Bordeaux F Ward De Ceuninck Univ. Limburgs Jorgen Moeltoft TU Denmark DK Andreas Preussger Infineon D Robert Thomas **Experts Network** USA Consolato Versace STMicroelectronics I Paolo Cova Univ Parma Christian Zardini Univ Bordeaux F

## Sub-Com ESD & Latch up

Antonio Andreini STMicroelectronics 1 Marise Bafleur LASS F Gianluca Boselli Texas Instruments USA Horst Gieser FhG D Ton Mouthaan Univ. Twente NL Wolfgang Stadler Infineon D Matthias Stecher Infineon D Wolfgang Wilkening Bosch  $\Box$ Lucia Zullino STMicroelectronics I

#### Reliability Dielectrics & Hot Carriers

F Xavier Avmerich Univ. Barcelona Francis Balestra F ENSERG Gérard Ghibaudo **ENSERG** F Gabriella Ghidini STMicroelectronics 1 Guido Groesenecken IMFC Giuseppe La Rosa IBM USA Hans Reisinger Infineon USA James Stathis IBM Nino Stojadinovic Univ. Nis Υ

# Interconnects Reliability

Barbara Zanderighi STMicroelectronics I

Andrea Scorzoni Univ. Perugia I

Fausto Fantini Univ. Modena I

#### Sub-Com TCAD for Reliability

Lars Bomholt ISE AG CH

Hervé Jaouen STMicroelectronics F

Gerhard Wachutka TU Munich D

# Sub-Com Power Devices & Automotive Reliability

| Giovanni Busatto  | Univ. Cassino      | 1  |

|-------------------|--------------------|----|

| Gérard Coquery    | INRETS             | F  |

| Leonardo Lonzi    | STMicroelectronics | 1  |

| Eckhardt Wolfgang | Siemens            | D  |

| Wolfgang Wondrak  | Daimler-Chrysler   | D  |

| Raymond Zehringer | ABB                | СН |

# Sub-Com Photonics & Compound Materials Reliability

| La aux Milata al Divina a a | District Diseases | _   |

|-----------------------------|-------------------|-----|

| Jean-Michel Dumas           | Univ. Limoges     | F   |

| Mattia Borgarino            | Univ. Modena      | I   |

| Hans Hartnagel              | TU Darmstadt      | D   |

| Nathalie Labat              | Univ. Bordeaux    | F   |

| Roberto Menozzi             | Univ. Parma       | I   |

| Giulia Salmini              | Pirelli           | - 1 |

| Bernd Witzigmann            | ETH Zürich        | CH  |

| Enrico Zanoni               | Univ. Padova      | - 1 |

# Sub-Com Failure Analysis Techniques

| Christian Boit     | TU Berlin      | D   |

|--------------------|----------------|-----|

| Jean-Pierre Fortea | CNES           | F   |

| Siegfried Görlich  | Infineon       | D   |

| Philippe Perdu     | CNES           | F   |

| Alan Street        | Qualcomm       | USA |

| Massimo Vanzi      | Univ. Cagliari | 1   |

#### Sub-Com EOBT

| Peter de Wolf   | Veeco           | USA       |

|-----------------|-----------------|-----------|

| Dionysz Pogany  | TU Vienna       | Α         |

| Ludwig Balk     | Univ. Wuppertal | D         |

| Ronald Cramer   | Altis           | F         |

| Wolfgang Mertin | Univ. Duisburg  | D         |

| Jacob Phang     | Univ Singapore  | Singapore |

## Sub-Com MEMs & Nanotechnology Reliability

| Ingrid de Wolf | IMEC           | В  |

|----------------|----------------|----|

| Wilfrid Claeys | Univ. Bordeaux | F  |

| Nico de Rooii  | Univ Neuchâtel | CH |

**ESREF 2004**, the 15th European Symposium on Reliability of Electron Devices will take place in Zurich (Switzerland) from 4 to 8 October 2004.

This international symposium continues to focus on recent developments and future directions in quality and reliability Management of materials, devices and circuits in microelectronics. It provides an open forum to develop all aspects of reliability management and advanced analysis techniques for present and future semiconductor applications. ESREF 2004 also includes the former Electron and Optical Beam Test Conference (EOBT) and it is co-sponsored by the IEEE Electron Device and IEEE Reliability Societies.

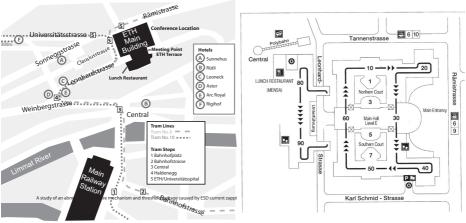

#### Conference Site

The conference takes place at the Swiss Federal Institute of Technology (ETH)

Main Building (Hauptgebäude)

Rämistrasse 101, CH-8092 Zurich, Switzerland

Phone +41 1 632 1111

#### Program Highlights

The Conference takes place from October 4 to 8, 2004 in the historical building of the Swiss Federal Institute of Technology (ETH) in Zurich, with the logistic support of the ETH and with the technical co-sponsorship of the IEEE Electron Device Society and of the IEEE Reliability Society.

The technical program of ESREF 2004 has been arranged to continue the tradition of the conference series while trying to identify the highlights of the fast evolving electronic device technology. In this perspective, the Symposium is opened by the keynote address of Shigeru Komatsu, Chief Knowledge and Technical Infrastructure Officer of the Toshiba Corp providing critical insight into the future of semiconductor manufacturing and related yield issues. Invited contributions address the state of the art of the R&D in fields of particular interest such as noise as reliability indicator, failures induced by cosmic radiation in power devices, time-resolved photon emission analysis, and as reliability challenges caused by ultra-low k interlevel dielectrics. Further subjects are covered by utorial courses on the use of Technology Computer Aided Design (TCAD) in reliability, on capabilities and limits of scanning probe techniques for semiconductors, on the implementation of virtual reliability qualification procedures, and on ESD testing. Finally, additional hot topics such as the efficiency of the most recent failure analysis techniques, and the optimum thermal management in power devices are debated in dedicated Workshops.

The 103 papers presented at this conference all passed a two-step reviewing process by the Technical Committee composed by nearly 50 worldwide reputated specialists from industry and academy. The logistic constraints imposed a three-day conference program with 41 papers proposed as posters and 62 as oral presentations. Poster and oral contributions have been organized in 11 technical sessions: Assembly Reliability, Compound Device Reliability, Power Device Reliability, Dielectrics Reliability, Failure Analysis & Advanced Characterization Techniques, Hot Carrier Reliability, Electron & Optical Beam Testing, Device, Circuits & MEMs Reliability, Electrostatic Discharges, Interconnects Reliability, and TCAD for Reliability. The last session on the use of Technology Computer Aided Design tools for reliability has been proposed for the first time, due to the increasing role played by device and process simulation in the implementation of built-in reliability programs in microelectronics.

ESREF 2004 improved the existing links with the sister conferences in reliability worldwide. In fact, this year the recipients of the Best Paper Award of the International Reliability Physics Symposium (IRPS, USA), of the Reliability Center of Japan Symposium (RCJ, Japan), and of the International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA, Singapore) have been invited in Zurich to present their results.

Finally, special attention has been paid to promote the technical and the human contacts among the participants of the Symposium. A special half-day networking event has been proposed, where all the attendees could meet each other in a pleasant and informal alpine environment at the lake of Lucerne.

The Proceedings of ESREF 2004 will be published as a special issue of the journal Microelectronics Reliability by the publisher Elsevier.

## **Tutorials**

Five tutorial courses are proposed before the beginning of the conference:

Monday October 4, 2004, 13:30 - 18:00

Room D 1.2

Tutorial 1. TCAD simulation tools for built in reliability in semiconductor devices

Chair: Chiara Corvasce, ETH Zürich

Speakers: Pavel Tichomirov and Lars Bomholt

Integrated Systems Engineering AG, Affolternstrasse 52, CH-8050 Zurich

Monday October 4, 2004, 13:30 - 15:00

Room D 7 2

Tutorial 2. Defect localization in ICs using laser techniques

Chair: Maria Stangoni, ETH Zürich

Speakers: Dean Lewis<sup>a</sup> and Philippe Perdu<sup>b</sup>

<sup>a</sup> IXL ENSEIRB CNRS UMR 5818, Université Bordeaux, Talence France

<sup>b</sup> CNES- French Space Agency, Toulouse France

Monday October 4, 2004, 15:30 - 18:00

Room D 7.2

Tutorial 3. Applications of Scanning Probe Microscopy for Failure Analysis

Chair: Maria Stangoni, ETH Zürich

Speaker: Peter De Wolf

VEECO INSTRUMENTS SAS. Dourdan France

Tuesday October 5, 2004, 08:30 – 10:30

Room D 1.2

Tutorial 4. Virtual Reliability Qualification

Chair: Valter Loll, Nokia Speaker: G.Q. Zhang

Technical University of Eindhoven and Philips Centre For Industrial

Technology, Eindhoven, The Netherlands

Tuesday October 5, 2004, 08:30 - 10:30

Tutorial 5. ESD Testing: HBM to very fast TLP

Room D 7.2

Chair: Luca Sponton, ETH Zürich

Speaker: Horst A. Gieser

Fraunhofer Institut für Zuverlässigkeit und Mikrointegration - IZM, München

## **Keynote Speech**

## A critical insight into the future semiconductor solutions

Shigeru Komatsu

Chief Knowledge & Technical Infrastructure Officer Toshiba Corporation, Japan

#### Invited contributions

#### Low frequency noise as a reliability diagnostic tool in compound semiconductor transistors

N. Labat, N. Malbert, C. Maneux, A. Touboul

IXL Laboratory - CNRS - ENSEIRB - University of Bordeaux, France

#### Reliability of power electronic devices against cosmic radiation-induced failure

G. Soelkner<sup>a</sup>, W. Kaindl<sup>b</sup>, H.-J. Schulze<sup>a</sup>, G. Wachutka<sup>b</sup>

## Time Resolved Photon Emission Processing Flow for IC Analysis

R. Desplats<sup>a</sup>, G. Faggion<sup>a</sup>, M. Remmach<sup>a</sup>, F. Beaudoin<sup>a</sup>, P. Perdu<sup>a</sup>, D. Lewis<sup>b</sup>

#### Reliability Challenges with Ultra-Low k Interlevel Dielectrics

J.R. Lloyd, M.R. Lane, X.-H. Liu, E. Liniger, T.M. Shaw, C.-K. Hu, R. Rosenberg IBM T.J. Watson Research Center, Yorktown Heights NY 10598, USA

#### The study of TDDB lifetime estimation for thin gate dielectrics (RCJ Best Paper Award)

Takeshi Shigeo, Kazuhiko Suzuki, Madoka Muta

System LSI Reliability Engineering Gr. System LSI Quality & Reliability Engineering Department, Toshiba Semiconductor Company, Japan

#### Negative Bias Temperature Instability in Triple Gate Transistors (IPFA Best Paper Award)

Shigenobu Maeda, Jung-A Choi, Jeong-Hwan Yang, You-Seung Jin, Su-Kon Bae, Young-Wug Kim, Kwang-Pyuk Suh

Technology Development Team, System LSI Division, Samsung Electronics, Korea

# Comparison of Oxide Breakdown Progression in Ultra-Thin Oxide SOI and Bulk pMOSFETs (IRPS Best Paper Award)

C. T. Chan, C. H. Kuo, C. J. Tang, M. C. Chen, Tahui Wang, S. Huang Lu\*, H.C. Hu\*, T.F. Chen\*, C.K. Yang\*, M.T. Lee\*, D.Y. Wu\*, J.K. Chen\*, S.C. Chien\*, S. W. Sun\*

Department of Electronics Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan \*Technology and Process Development Division, UMC, Hsin-Chu, Taiwan

<sup>&</sup>lt;sup>a</sup> Infineon Technologies, Germany

b Institute for Physics of Electrotechnology, Munich University of Technology, Germany

<sup>&</sup>lt;sup>a</sup> CNES-Thales Laboratory, French Space Agency, France

b IXL Laboratory, 351 cours de la Libération, 33405 Talence Cedex – France

## **Conference Program**

Tuesday, October 5

11:00 Opening

11:25 Keynote Speech

Auditorium Maximum

"A critical insight into the future semiconductor solutions"

Shigeru Komatsu

Chief Knowledge & Technical Infrastructure Officer Toshiba Corporation, Japan

12:20 Lunch

#### Session Assembly Reliability (Asbl)

Auditorium Maximum

Co-chairs: J. Moltoft, Technical Univ. of Denmark, W. Gerling, Consultant

14:15 Characterization and fatigue damage simulation in SAC solder joints

M.Erinc, P.J.G.Schreurs, G.Q.Zhang, M.G.D.Geers

Materials Technology, Department of Mechanical Engineering, Eindhoven University of Technology, The Netherlands

14:40 Effect of long and short Pb-free soldering profiles of IPC/JEDEC J-STD-020 on plastic SMD packages

P. Alperna, K.C. Leeb and R. Tilgnera

<sup>a</sup> Infineon Technologies, Corporate Assembly and Testing, Germany

<sup>b</sup> Infineon Technologies Asia Pacific, Product Reliability and Analysis, Singapore

15:05 Reliability of Low-Cost PCB Interconnections for Telecommunication Applications G. Duchamp, F. Verdier, Y. Deshayes, F. Marc, Y. Ousten, Y. Danto Laboratoire IXL – ENSEIRB – UMR CNRS 5818, 33405 Talence, France

15:30 Effect of bonding pressure on reliability of flip chip joints on flexible and rigid substrates

L. Frisk, A. Seppälä and E. Ristolainen

Institute of Electronics. Tampere University of Technology. 33101 Tampere. Finland

15:55 How to study delamination in plastic encapsulated devices

Hélène Frémont<sup>a</sup>, Jean-Yves Delétage<sup>a</sup>, Kirsten Weide-Zaage<sup>b</sup>, Yves Danto<sup>a</sup> IXL - ENSEIRB - CNRS, University of Bordeaux, France

b Laboratorium für Informationstechnologie, University of Hannover, Germany

#### Break

16:50 Characterization and Modelling of Moisture Driven Interface Failures

*M.A.J. van Gils<sup>a</sup>*, *P.J.J.H.A. Habets<sup>b</sup>*, *G.Q. Zhang<sup>ab</sup>*, *W.D. van Driel<sup>a</sup>*, *P.J.G. Schreurs<sup>b</sup>*<sup>a</sup> Philips, P.O. Box 218, 5600 MD, Eindhoven, The Netherlands

<sup>b</sup> Eindhoven University of Technology, The Netherlands

17:15 Metal migration in epoxy encapsulated ECL devices

C. Zhang, P. Yalamanchili, M. Al-Sheikhley and A. Christou Materials Science and Engineering and Reliability Engineering Center, University of Maryland, USA

#### Session Compound Reliability (Comp)

Room D 7.2

Co-Chairs: E. Zanoni, University of Padova, A. Touboul, University of Bordeaux

14:30 Low frequency noise as a reliability diagnostic tool in compound semiconductor transistors (INVITED)

N. Labat, N. Malbert, C. Maneux, A. Touboul IXL Laboratory - CNRS - ENSEIRB, University of Bordeaux, France

15:05 Reliability Investigation of Gallium Nitride HEMT

A.  $Sozza^{abc}$ , C.  $Dua^a$ , E.  $Morvan^a$ , B.  $Grimbert^d$ , V.  $Hoel^d$ , S.L.  $Delag^{ae}$ , N.  $Chaturvedi^d$ , R.  $Lossy^d$ , J.  $Wuerfl^d$

<sup>a</sup> TRT/Tiger, France

<sup>b</sup> DEI, Università degli Studi di Padova, Italy

<sup>C</sup> IXL Laboratory, University of Bordeaux, France

d IEMN/Tiger, France

<sup>e</sup> FBH, Ferdinand-Braun-Institut fuer Hoechstfrequenztechnik, 12489 Berlin, Germany

15:30 Hot carrier aging degradation phenomena in GaN based MESFETs

F. Rampazzo<sup>a</sup>, R. Pierobon<sup>a</sup>, D. Pacetta<sup>a</sup>, C. Gaquiere<sup>b</sup>, D.Theron<sup>b</sup>, B. Boudart<sup>c</sup>, G. Meneghesso<sup>a</sup>, E. Zanoni<sup>a</sup>

<sup>a</sup> University of Padova, Department of Information Engineering, and INFM - UdR Padova, Italy

<sup>b</sup> Institut d'Eletronique et de Microelectronique du Nord, CNRS 8520, Départment Hyperfréquences et Semiconducteurs, France

<sup>c</sup> Laboratoire Universitaire de Science Appliquées de Chebourg, France

15:55 Temperature-dependent breakdown and hot carrier stress of PHEMTs

P. Cova, N. Delmonte, G. Sozzi, R. Menozzi Dipartimento di Ingegneria dell'Informazione, University of Parma, Italy

#### Break

16:50 On-wafer low frequency noise measurements of SiGe HBTs: Impact of technological improvements on 1/f noise

B. Grandchamp, C. Maneux, N. Labat, A. Touboul, T. Zimmer IXL Laboratory - CNRS - ENSEIRB, University of Bordeaux, France

Gallery Floor F

#### A. Assembly Reliability

Influence of the thermo-mechanical residual state on the power assembly modellization

Alexandrine Guédon-Gracia, Pascal Roux, Eric Woirgard, Christian Zardini Laboratoire IXL - CNRS - ENSEIRB - University of Bordeaux, France

Study of influence of failure modes on lifetime distribution prediction of 1.55 µm DFB Laser diodes using weak drift of monitored parameters during ageing tests

```

L. Mendizabala, L. Bechoua, Y. Deshayesa, F. Verdiera, Y. Dantoa, D. Laffitteb,

```

J.L. Goudard<sup>b</sup>, F. Houé<sup>b</sup>

<sup>a</sup> IXL Laboratory, University of Bordeaux, France

<sup>b</sup> AVANEX-France, France

Comparative study of thermal cycling and thermal shocks tests on electronic components reliability

S. Moreau<sup>ab</sup>, T. Lequeu<sup>a</sup>, R. Jérisian<sup>a</sup>

<sup>a</sup> LMP. France

<sup>b</sup> STMicroelectronics. France

Integrated thermo-mechanical design and qualification of wafer backend structures

G.Q. Zhang<sup>a</sup> and J. Bisschop<sup>b</sup>

<sup>a</sup> Eindhoven University of Technology and Philips Centre for Industrial Technology, The Netherlands

<sup>b</sup> Philips Semiconductors, The Netherlands

Non destructive control of flip chip packages for space applications

M. Paillarda, C. Schaffausera, C. Drevona, J.L. Cazauxa, H.R. Schubachb, F. Freseb

<sup>a</sup> Alcatel Space, 26 Avenue Champollion, BP1187, F-31037 Toulouse, France

<sup>b</sup> Dantec Ettemeyer GmbH, Kaessbohrer Str. 18, D-89077 Ulm, Germany

#### B. Failure Analyisis & Advanced Characterization Techniques

Current crowding in faulty MOSFET: optical and electrical investigation

A. Tosi<sup>a</sup>. F. Stellari<sup>b</sup>. F. Zappa<sup>a</sup>

<sup>a</sup> Politecnico di Milano, Dipartimento di Elettronica e Informazione, Italy

b IBM T.J. Watson Research Center, Yorktown Heights – NY 10598 (USA)

Gallium Artefacts on FIB-milled Silicon Samples

Joachim C. Reiner, Philipp Nellen, Urs Sennhauser

EMPA - Electronics/Metrology Laboratory, Switzerland

VCO phase noise improvement through direct passive component modification in the FIB

B. Domengès<sup>a</sup>, B. Tiphaigne<sup>b</sup>

<sup>a</sup> LAMIP, laboratoire de microélectronique ISMRA-Philips, France

b STEPMIND OUEST. France

Failure analysis of vertical cavity surface emission laser diodes

F. Siegelin

Infineon Technologies, Germany

Failure analysis of RFIC Amplifiers

- G. Mura<sup>a</sup>, M. Vanzi<sup>a</sup>, G. Micheletti<sup>b</sup>

- <sup>a</sup> Department of Electric and Electronic Engineering DIEE-INFM, University of Cagliari, Italy

- <sup>b</sup> Datalogic S.p.A, Bologna, Italy

Femtosecond Laser Ablation for Backside Silicon Thinning

- F. Beaudoin<sup>a</sup>, J. Lopez<sup>b</sup>, M. Faucon<sup>b</sup>, R. Desplats<sup>a</sup>, P. Perdu<sup>a</sup>

- <sup>a</sup> CNES-THALES Laboratory, France

- <sup>b</sup> CELIA-PALA UMR 5107 University of Bordeaux, France

A Novel Automatic Polishing Technique for Micro-Controllers with 450 off Si <100> Rotation

- I. Grimberg<sup>a</sup>, H. Coulson<sup>b</sup>, K. Williamson<sup>b</sup>, J. Pohl<sup>b</sup>, Z. Shafrir<sup>a</sup>, E. Raz<sup>a</sup>

- a Sagitta Ltd. Israel

- b ATMEL. United Kingdom

- AFM-based scanning capacitance techniques for deep sub-micron semiconductor failure analysis

Guenther Benstetter<sup>a</sup>. Peter Breitschopf<sup>a</sup>. Werner Frammelsberger<sup>a</sup>. Heiko Ranzinger<sup>a</sup>. Peter Reislhuber<sup>a</sup>. Thomas Schweinboeck<sup>C</sup>

- <sup>a</sup> University of Applied Sciences Deggendorf, Germany

- <sup>b</sup> University of the West of England, Bristol, United Kingdom

- <sup>c</sup> Infineon Technologies, Germany

On the Use of Neural Networks to Solve the Reverse Modelling Problem for the Quantification of Dopant Profiles Extracted by Scanning Probe Microscopy Techniques

- Mauro Ciappa<sup>a</sup>, Maria Stangoni<sup>a</sup>, Wolfgang Fichtner<sup>a</sup>, Elisa Ricci<sup>b</sup> and Andrea Scorzoni<sup>b</sup> <sup>a</sup> Swiss Federal Institute of Technology (ETH) Zurich, Integrated Systems Laboratory,

- b University of Perugia, Faculty of Engineering, Italy

Investigation of SEU sensitivity of Xilinx Virtex II FPGA by pulsed laser fault injections

- R. Desplats<sup>a</sup>, S. Petit<sup>c</sup>, S. Rezgui<sup>d</sup>, C. Carmichael<sup>d</sup>, P. Fouillat<sup>b</sup>, D. Lewis<sup>b</sup>

- <sup>a</sup> CNES- French Space Agency, 18, avenue Edouard Belin 31401 Toulouse France

- b IXL Laboratory, 351 cours de la Libération, 33405 Talence Cedex France

- <sup>c</sup> CONERA, 2, avenue Edouard Belin, 31400 Toulouse France

- <sup>d</sup> Xilinx, Group HI-REL, Aerospace & Defense Products, USA

- Light Emission From Small Technologies. Are Silicon Based Detectors Reaching Their Limits?

M. Remmach<sup>a</sup>, R. Desplats<sup>a</sup>, P. Perdu<sup>a</sup>, J. P. Roux<sup>b</sup>, M. Vallet<sup>b</sup>, S. Dudit<sup>c</sup>, P. Sardin<sup>c</sup>, D Lewis<sup>d</sup>

- a CNES French Space Agency, France

- <sup>b</sup> NPTest Inc. USA

- <sup>c</sup> ST Microelectronics, France

- d IXL Laboratory, France

- Field Failure Mechanism Investigation of GaAs based HBT Power Amplifier Module (PAM)

Jae-Seong Jeong, Jong-Shin Ha, Sang-Deuk Park

Advanced Technology Group, CS Management Center, Samsung, Korea

## C. Power Device Reliability

Reliability study of Power RF LDMOS for Radar application

H. Maanane<sup>a</sup>, P. Bertram<sup>b</sup>, J. Marcon<sup>a</sup>, M. Masmoudi<sup>a</sup>, M. Belaid<sup>a</sup>, K. Mourgues<sup>a</sup>,

P. Eudeline<sup>b</sup> and K. Ketata<sup>a</sup>

<sup>a</sup> LEMI, University of Rouen, France

b THALES Air Defence, France

Experimental characterization of temperature distribution on Power MOS devices during Unclamped Inductive Switching

E. D'Arcangelo, A. Irace, G. Breglio and P. Spirito

Dipartimento di Ingegneria Elettronica e delle Telecomunicazioni,

Università degli Studi di Napoli "Federico II", Italy

Comparison Between the Behaviour of Punch-Through and Non-Punch-Through Insulated Gate Bipolar Transistors Under High Temperature Reverse Bias Stress

C. O. Maiga, H. Toutah, B. Tala-Ighil, B. Boudart Site Universitaire, LUSAC, Cherbourg-Octeville, France.

Passivation schemes to improve power devices HAST robustness

L. Alliranda, B. Regairazb

<sup>a</sup> T&M organization ,Technology Solutions, FREESCALE SAS, France

<sup>b</sup> T&M organization, Die Manufacturing MOS20, FREESCALE SAS, France

Enhancement of breakdown voltage for Ni-SiC Schottky diodes utilizing field plate edge termination

T. Ayalew, A. Gehring , T. Grasser, and S. Selberherr

Christian-Doppler-Laboratory for TCAD in Microelectronics, Institute for Microelectronics, TU Vienna, Austria

Compare of SOI and SOS LIGBT structure for the thermal conductivity and self-heating characteristics

J. Y. Kim<sup>a</sup>, S. W. Park<sup>a</sup>, M. C. Jung<sup>a</sup>, C. H. Kim<sup>a</sup>, M. Y. Sung<sup>a</sup>, D. H. Rhie<sup>b</sup>, E. G. Kang<sup>c</sup>, N. G. Kim<sup>c</sup>, S. C. Kim<sup>d</sup>

<sup>a</sup> Department of Electrical Engineering, Korea University, Korea

<sup>b</sup> Department of Electrical Engineering, Suwon University, Korea

<sup>c</sup> Department of Electronic Enginnering, Far East University, Korea

d Korea Electrotechnology Search Institute, Korea

Analysis of wire bond and metallization degradation mechanisms in DMOS power transistors stressed under thermal overload conditions

Th. Detzel, M. Glavanovics, K. Weber

Infineon Technologies Austria AG, Siemensstrasse 2, A-9500 Villach

## D. Dielectrics & hot carriers reliability

A new approach to the modeling of oxide breakdown on CMOS circuits

R. Fernández, R. Rodríguez, M. Nafría, X. Aymerich

Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, Spain

Standard and C-AFM tests to study the post-BD gate oxide conduction of MOS devices after current limited stresses.

M. Porti, S. Meli, M. Nafría, X. Aymerich

Dept. Enginyeria Electrònica, Universitat Autònoma de Barcelona, Spain

Time dependent dielectric breakdown in a low-k interlevel dielectric

J.R. Lloyd $^a$ , E. Liniger $^a$ , S.T. Chen $^b$

<sup>a</sup> IBM T.J. Watson Research Center, USA

b IBM Microelectronics. USA

On the defects introduced by AC and DC hot carrier stress in SOI PD MOSFETs

M.Exarchos<sup>a</sup>, F.Dieudonne<sup>b</sup>, J.Jomaah<sup>b</sup>, G.J.Papaioannou<sup>a</sup> and F.Balestra<sup>b</sup>

<sup>a</sup> University of Athens, Physics Dept., Solid State Physics Section, Greece

b IMEP (UMR CNRS/INPG/UJF). France

Reduced Hot Carrier Effects in Self-Aligned Ground-Plane FDSOI MOSFET's

Se Re Na Yun<sup>a</sup>, Chong Gun Yu<sup>a</sup>, Seok Hee Jeon<sup>a</sup>, Chung Kyue Kim<sup>b</sup>, Jong Tae Park<sup>a</sup>, and Jean Pierre Colinge<sup>c</sup>

a Department of Electronics Engineering, University of Incheon, Korea

b Department of Computer Engineering, University of Incheon, Korea

<sup>c</sup> Department of Electrical and Computer Engineering, University of California, USA

# E. Device & circuit reliability

A new structure to monitor electrical transients during programming of EEPROM memory cells

N. Babouxa, C. Plossua, P. Boivinb

<sup>a</sup> Laboratoire de Physique de la Matière, France

<sup>b</sup> STMicroelectronics. France

Evaluation of STI degradation using temperature dependence of leakage current in parasitic STI MOSFET

Oleg Semenov<sup>a</sup>, Michael Obrecht<sup>b</sup> and Manoj Sachdev<sup>a</sup>

<sup>a</sup> Dept. of Electrical and Computer Engineering, University of Waterloo, Canada

<sup>b</sup> Siborg Systems Inc., 24 Combermere Crescent, Canada

Reliability determination of aluminium electrolytic capacitors by the mean of various methods. Application to the protection system of the LHC

F. Perisse<sup>a</sup>, P. Venet<sup>b</sup>, G. Rojat<sup>b</sup>

<sup>a</sup> LEA Boulevard Marie & Pierre CURIE, France

<sup>b</sup> CEGELY UCB Lvon. France

Failure Analysis of RuO2 Thick Film Chip Resistors

S.Podda<sup>a</sup>, G.Cassanelli<sup>b</sup>, F.Fantini<sup>b</sup>, M.Vanzi<sup>a</sup>

<sup>a</sup> Department of Electronic Engineering, University of Cagliari, Italy

<sup>b</sup> University of Modena e Reggio Emilia Dipartimento di Ingegneria dell'Informazione, Italy

First step in the reliability assessment of ultracapacitors used as power source in hybrid electric vehicles

W. Lajnef, J.M. Vinassa, S. Azzopardi, O. Briat, C. Zardini

IXL Laboratory, University of Bordeaux, France

## F. Electrostatic discharges

Study and validation of a power-rail ESD clamp in BiCMOS process with a reduced temperature dependency of its leakage current

F. Barbier<sup>ae</sup>, F. Blanc<sup>a</sup>, A. Le Grontec<sup>a</sup>, R. Colclaser<sup>b</sup>, T. Smedes<sup>c</sup>, M. Johnson<sup>d</sup>,

S. Bardy<sup>a</sup>, P. Descamps<sup>e</sup>

<sup>a</sup> Philips Semiconductors Caen. France

<sup>b</sup> Philips Semiconductors Fishkill, USA

<sup>c</sup> Philips Semiconductors Niimegen. The Netherlands

<sup>d</sup> Philips Semiconductors San Jose, USA

<sup>e</sup> LaMIP, Laboratoire de Microélectronique ENSI Caen-Philips, France

The Failure Analysis of High Voltage Tolerance IO Buffer under ESD

Tao Cheng, Y.S. Shyu Media Tek Inc.. Taiwan

Study of the ESD defects impact on ICs reliability

F. Essely<sup>a</sup>, C. Bestory<sup>c</sup>, N. Guitard<sup>b</sup>, M. Bafleur<sup>b</sup>, A. Wislez<sup>c</sup>, E. Doche<sup>c</sup>, P. Perdu<sup>d</sup>,

A. Touboul<sup>a</sup>, D. Lewis<sup>a</sup>

<sup>a</sup> XL Laboratory, University of Bordeaux, France

b LAAS-CNRS, France

<sup>c</sup> LCIE, France

<sup>d</sup> CNES-Thales Laboratory, France

The Impact of CMOS technology scaling on MOSFETs second breakdown: Evaluation of ESD robustness

O. Semenov<sup>a</sup>, H. Sarbishaei<sup>a</sup>, V. Axelrad<sup>b</sup> and M. Sachdev<sup>a</sup>

<sup>a</sup> Dept. of Electrical and Computer Engineering, University of Waterloo, Canada

<sup>b</sup> Seguoia Design Systems, USA

A case study of ESD failures at random levels: analysis, explanation and solution

T. Wu<sup>ab</sup>, T. Smedes<sup>b</sup>, J.P. Lokker<sup>b</sup>, S-N. Mei<sup>c</sup>, J.W. Slotboom<sup>a</sup>

<sup>a</sup> Delft University of Technology, Mekelweg 4, 2628 CD Delft, the Netherlands

<sup>b</sup> Philips Semiconductors, Gerstweg 2, 6534 AE Nijmegen, the Netherlands

<sup>c</sup> Philips Semiconductors, Fishkill, 2070 Route 52, Hopewell Junction, NY, USA

A study of an abnormal ESD failure mechanism and threshold voltage caused by ESD current zapping sequence

Yong-Ha Song, Choong-Kyun Kim, Moo-Young Park, Bum-Suk Kye, Jeong-Il Seo, Dong-Soo Cho. Taek-Soo Kim, Gab-Soo Han

ASIC Development Team, System LSI Division, Semiconductor Business, Samsung, Korea

#### Session Power Device Reliability (Pow)

Auditorium Maximum

Co-chairs: E. Wolfgang, Siemens, A. Hamidi, ABB

- 8:30 Reliability of power electronic devices against cosmic radiation-induced failure (INVITED)

- G. Soelkner<sup>a</sup>, W. Kaindl<sup>b</sup>, H.-J. Schulze<sup>a</sup>, G. Wachutka<sup>b</sup>

- <sup>a</sup> Infineon Technologies, Automotive & Industrial, Germany

- b Inst. for Physics of Electrotechnology, Munich University of Technology, Germany

- 9:10 The Role of the Parasitic BJT Parameters on the Reliability of New Generation Power MOSFET during Heavy Ion Exposure

- F. Velardí<sup>a</sup>, F. Iannuzzo<sup>a</sup>, G. Busatto<sup>a</sup>, A. Porzio<sup>a</sup>, A. Sanseverino<sup>b</sup>, G. Currò<sup>c</sup>, A. Cascio<sup>c</sup>, F. Frisina<sup>c</sup>

- <sup>a</sup> D.A.E.I.M.I., Università degli Studi di Cassino, Italy

- <sup>b</sup> D.I.E.T., Università degli Studi di Napoli, Italy

- <sup>c</sup> ST-Microelectronics, Italy

- 9:35 Semiconductors in high temperature applications a future trend in automotive industry Michael Goroll<sup>a</sup>, Reinhard Pufall<sup>a</sup>, Werner Kanert<sup>a</sup>, Boris Plikat<sup>b</sup>

- <sup>a</sup> Infineon Technologies AG, Automotive & Industrial Division, Germany

- b Infineon Technologies AG, Corporate Assembly & Test Division, Germany

- 10:00 Analysis of PowerMOSFET chips failed in thermal instability

- A. Castellazzi<sup>a</sup>, H. Schwarzbauer<sup>b</sup>, D. Schmitt-Landsiedel<sup>c</sup>

- <sup>a</sup> Institute of Physics of Electrotechnology, Munich University of Technology, Germany

- <sup>b</sup> Siemens, Germany

- <sup>c</sup> Institute of Technical Electronics, Munich University of Technology, Germany

#### Break

- 10:55 Partial Discharge Failure Analysis of AlN Substrates for IGBT Modules J.-H. Fabian, S. Hartmann, A. Hamidi ABB Switzerland Ltd, Corporate Research, CH-5405 Baden-Dättwil, Switzerland

- 11:20 Investigation of IGBT turn-on failure under high applied voltage operation

Masayasu Ishiko<sup>a</sup>, Koji Hotta<sup>b</sup>, Sachiko Kawaji<sup>a</sup>, Takahide Sugiyama<sup>a</sup>, Tomoyuki Shouji<sup>a</sup>, Takeshi Fukami<sup>b</sup>, Kimimori Hamada<sup>b</sup>

- <sup>a</sup> Power Device Lab., Toyota Central R&D Labs., Japan

- <sup>b</sup> Electronics Engineering Div. III, Toyota Motor Corporation, Japan

- 11:45 High reliable high power diode for welding applications

- P. Cova<sup>a</sup>, F. Fasce<sup>b</sup>, P. Pampili<sup>b</sup>, M. Portesine<sup>b</sup>, G. Sozzi<sup>a</sup>, P.E. Zani<sup>b</sup>

- a Dipartimento di Ingegneria dell'Informazione. University of Parma. Italy

- b POSEICO S.p.A. via N. Lorenzi, 8 16152 Genova, Italy

- 12:10 Analysis and optimisation through innovative driving strategy of high power IGBT performances/EMI reduction trade-off for converter systems in railway applications

- G. Busatto<sup>a</sup>, L. Fratelli<sup>b</sup>, C. Abbate<sup>a</sup>, R. Manzo<sup>a</sup>, F. Iannuzzo<sup>a</sup>

- <sup>a</sup> Dept. of Automation, Electromagnetism, Information Engineering and Industrial Mathematics, University of Cassino, Italy

- b AnsaldoBreda Spa, Italy

#### Lunch

Chair: G. Groesenecken, IMEC

9:10 The study of TDDB lifetime estimation for thin gate dielectrics (INVITED, Best Paper Award RCJ Symposium)

Takeshi Shigeo, Kazuhiko Suzuki, and Madoka Muta System LSI Reliability Eng. Gr. System LSI Quality & Reliability Eng. Dept., Toshiba Semiconductor Company. Japan

9:35 Mie-Grüneisen Analysis of the Molecular Bonding States in Silica Which Impact Time-Dependent Dielectric Breakdown

J.W. McPherson

Silicon Technology Development, Texas Instruments, USA

10:00 Extraction of the trap distribution responsible for SILCs in MOS structures from measurements and simulations of DC and noise properties

A.Nannipieriab, G. lannacconeb, F. Crupic

<sup>a</sup> ISE Integrated Systems Engineering AG, Switzerland

b Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazio ni, Universita' degli Studi di Pisa and IEIIT-CNR. Italy

<sup>c</sup> Dipartimento di Elettronica, Informatica e Sistemistica, University of Calabria, Italy

#### Break

10:55 Comparison of Oxide Breakdown Progression in Ultra-Thin Oxide SOI and Bulk pMOSFETs (INVITED, Best Paper Award IPFA)

C. T. Chan<sup>a</sup>, C. H. Kuo<sup>a</sup>, C. J. Tang<sup>a</sup>, M. C. Chen<sup>a</sup>, T. Wang<sup>a</sup>, S. H. Lu<sup>b</sup>, H. C. Hu<sup>b</sup>, T. F. Chen<sup>b</sup>, C. K. Yang<sup>b</sup>, M. T. Lee<sup>b</sup>, D. Y. Wu<sup>b</sup>, J. K. Chen<sup>b</sup>, S. C. Chien<sup>b</sup>, and S. W. Sun<sup>b</sup>

<sup>a</sup> Department of Electronics Engineering, National Chiao-Tung University, Taiwan

<sup>b</sup> Technology and Process Development Division, UMC, Taiwan

11:20 Plasma Charging Damage Reduction in IC Processing by A Self-balancing Interconnect

Z. Wang<sup>ab</sup>, J. Ackaert<sup>b</sup>, C. Salm<sup>a</sup>, F. G. Kuper<sup>ab</sup>, E. De Backer<sup>b</sup>

<sup>a</sup> MESA+ Research Institute / University of Twente, Semiconductor Components Group, The Netherlands

<sup>b</sup> AMI Semiconductor, Belgium

11:45 Effect of Pre-Existing Defects on Reliability Assessment of High-K Gate Dielectrics

G. Bersuker, J. H. Sim, C. D. Young, R. Choi, P. M. Zeitzoff, G. A. Brown, B. H. Lee, R. W. Murto

International SEMATECH.USA

12:10 Reliability of High-K Dielectrics and Its Dependence on Gate Electrode and Interfacial / High-K Bi-Layer Structure

Y. H. Kim<sup>a</sup>\*, R. Choi<sup>a</sup>, R. Jha<sup>b</sup>, J., Lee<sup>b</sup>, V. Misra<sup>b</sup>, and J. C. Lee<sup>a</sup>

<sup>a</sup> Microelectronics Research Center, Department of Electrical and Computer Engineering, The University of Texas, USA

b Dept. of ECE, North Carolina State University, USA

\* now with IBM, USA

#### Lunch

# Wednesday, October 6

## Session Failure Analysis & Advanced Characterization Techniques (Fa) Auditorium Maximum

Co-chairs: M. Vanzi, University of Cagliari, A. Street, Qualcomm

14:15 Implementation of TRE systems into Emission Microscopes

A. Tosia, M. Remmachb, R. Desplatsb, F. Zappaa, P. Perdub

a Politecnico di Milano, Dipartimento di Elettronica e Informazione, Italy

<sup>b</sup> CNES- French Space Agency, France

14:40 Overcoming Fault Test Coverage with Time-Resolved Emission (TRE) Probing

Steven Kasapi<sup>a</sup> and Bruce Cory<sup>b</sup>

<sup>a</sup> Credence Systems Corporation, 1421 California Circle Milpitas, CA 95035

<sup>b</sup> NVIDIA Corporation, 2701 San Tomas Expressway, Santa Clara, CA 95050

15:05 New trends in the application of Scanning Probe Techniques in Failure Analysis

T. Schweinböck<sup>a</sup>, S. Schömann<sup>a</sup>, D. Alvarez<sup>ab</sup>, M. Buzzo<sup>cd</sup>, W. Frammelsberger<sup>ef</sup>,

P. Breitschopf<sup>e</sup>, G. Benstetter

<sup>a</sup> Infineon Technologies AG, Germany

b IMEC, Belgium

<sup>c</sup> Infineon Technologies AG, Austria

<sup>d</sup> Swiss Federal Institute of Technology (ETH) Zurich, Integrated Systems Laboratory, Switzerland

<sup>e</sup> University of Applied Sciences Deggendorf, Germany

f University of the West of England, UK

15:30 Quantitative 3D reconstruction from BS imaging

R. Pintus, S. Podda, F. Mighela and M. Vanzi

University of Cagliari, Department of Electrical and Electronic Engineering, Italy

15:55 Automated Diagnosis and Probing Flow for Fast Fault Localization in IC

D.Martin<sup>a</sup>, R.Desplats<sup>b</sup>, G.Haller<sup>a</sup>, P.Nouet<sup>c</sup>, F.Azaïs<sup>c</sup>

<sup>a</sup> ST Microelectronics, Z.I. de Rousset, 13106 Rousset, France

<sup>b</sup> CNES laboratory – bpi 141418, avenue Edouard Belin, 31401 Toulouse, France

<sup>c</sup> LIRMM, University of Montpellier, France

#### Break

16:50 Magnetic Microscopy for IC Failure Analysis: Comparative Case Studies using SQUID, GMR and MTJ systems

Olivier Crépel<sup>a</sup>, Patrick Poirier<sup>a</sup>, Philippe Descamps<sup>a</sup>, Romain Desplats<sup>b</sup>, Philippe Perdu<sup>b</sup>, Gérald Haller<sup>c</sup>, Abdelhatif Firiti<sup>c</sup>

<sup>a</sup> LaMIP. Philips Semiconductors. France

<sup>b</sup> CNES- French Space Agency, France

<sup>c</sup> ST Microelectronics, France

17:15 Study on electrostatic discharge (ESD) reliability improvement of ZnO-based multilayered chip varistor(MLV)

M. H. Ji, C. H. Choi, B. K. Jang, B. K. Kim

Central R&D Institue, Samsung Electro-Mechanics, Korea

17:40 Fail / Recover / Fail (F/R/F) failure mechanisms new trend

C. Ali, C. Charpentier

Texas Instruments France, France

## Session Hot Carrier Reliability (Hc)

Room D 7.2

Chair: N. Stojadinovic, University of Nis

14:15 Negative Bias Temperature Instability in Triple Gate Transistors (INVITED, Best Paper Award IRPS)

Shigenobu Maeda, Jung-A Choi, Jeong-Hwan Yang, You-Seung Jin, Su-Kon Bae, Young-Wug Kim, and Kwang-Pyuk Suh

Technology Development Team, System LSI Division, Samsung Electronics, Korea

14:40 Evidence for source side injection hot carrier effects on lateral DMOS transistors

S. Aresu<sup>b</sup>, , W. De Ceuninck<sup>ab</sup>, G. Van den bosch<sup>c</sup>, G. Groeseneken<sup>cd</sup>, P. Moens<sup>e</sup>,

J. Mancaab, D. Wojciechowskie, P. Gassote

<sup>a</sup> Limburgs University Centre, Institute for Materials Research, Belgium

b IMEC vzw, division IMOMEC, Belgium

<sup>c</sup> IMEC vzw, Belgium

d Katholieke Universiteit Leuven, ESAT Departments, Belgium

<sup>e</sup> AMI Semiconductor Belgium BVBA, Belgium

15:05 Locating hot carrier injection in n-type DeMOS transistors by Charge Pumping and 2D device simulations

F. Bauwens and P. Moens

Technology R&D, AMI Semiconductor Belgium BVBA, Belgium

15:30 Effects of hot carrier and irradiation stresses on advanced excimer laser annealed polycrystalline silicon thin film transistors

D.N. Kouvatsos<sup>a</sup>, V. Davidovic<sup>b</sup>, G.J. Papaioannou<sup>c</sup>, N. Stojadinovic<sup>b</sup>, L. Michalas<sup>c</sup>, M. Exarchos<sup>c</sup>, A.T. Voutsas<sup>d</sup> and D. Goustouridis<sup>a</sup>

a Institute of Microelectronics. Greece

<sup>b</sup> Faculty of Electronic Engineering, University of Nis, Serbia and Montenegro

<sup>c</sup> Solid State Section, Physics Department, University of Athens, Greece

<sup>d</sup> LCD Process Technology Laboratory, Sharp Labs of America, Inc., USA

15:55 Effects of hot carrier stress on the RF performance in SOI MOSFETs

Byung-Jin Lee, Kyosun Kim, and Jong-Tae Park

Department of Electronics Engineering, University of Incheon, Korea

#### Break

18:10 Workshop Power Reliability

Auditorium Maximum

Thermal management: How to get rid of the heat?

Coordinators: E. Wolfgang, Siemens AG, Germany

W. Wondrak, Daimler Chrysler, Germany

18:10 Workshop Eufanet

Room D 7.2

Submicron 3D localization and imaging Coordinator: P. Perdu, CNES

Thursday, October 7

#### Session Electron & Optical Beam Testing, Advanced Techniques (EOBT) Auditorium Maximum

Chair: L. Balk, University of Wuppertal

8:30 Time Resolved Photon Emission Processing Flow for IC Analysis (INVITED)

R. Desplats<sup>a</sup>, G. Faggion<sup>a</sup>, M. Remmach<sup>a</sup>, F. Beaudoin<sup>a</sup>, P. Perdu<sup>a</sup>, D. Lewis<sup>b</sup>

<sup>a</sup> CNES-Thales lab. French Space Agency, France

<sup>b</sup> IXL Laboratory, France

9:10 Testing of Ultra Low Voltage VLSI Chips using the Superconducting Single-Photon Detector (SSPD)

Franco Stellari and Peilin Song

IBM T.J. Watson Research Center, USA

9:35 Interactive and non-destructive verification of SRAM-descrambling with laser

A Stuffer

Department of Failure Analysis, Infineon AG, Munich

10:00 Understanding the effects of NIR Laser Stimulation on NMOS transistor

A. Firiti<sup>a</sup>, F. Beaudoin<sup>b</sup>, G. Haller<sup>a</sup>, P. Perdu<sup>b</sup>, D. Lewis<sup>c</sup>, P. Fouillat<sup>c</sup>

<sup>a</sup> ST Microelectronics, 13106 Rousset, France

<sup>b</sup> CNES-Thales laboratory, France

<sup>c</sup> IXL Laboratory. France

#### Break

10:55 2D Dopant Profiling on 4H Silicon Carbide P+N Junction by Scanning Capacitance and Scanning Electron Microscopy

Marco Buzzo<sup>ab</sup>, Markus Leicht<sup>a</sup>, Thomas Schweinböck<sup>c</sup>, Mauro Ciappa<sup>b</sup>,

Maria Stangoni<sup>b</sup>, Wolfgang Fichtner<sup>b</sup>

<sup>a</sup> Infineon Technologies AG, Villach, Austria

b Swiss Federal Institute of Technology (ETH), Integrated Systems Laboratory, Switzerland

<sup>c</sup> Infineon Technologies AG, Munich, Germany

11:20 Transient interferometric mapping of smart power SOI ESD protection devices under TLP and vf-TLP stress

S. Bychikhin<sup>a</sup>, V. Dubec<sup>a</sup>, D. Pogany<sup>a</sup>, E. Gornik<sup>a</sup>, M. Graf<sup>b</sup>, V. Dudek<sup>b</sup>, W. Soppa<sup>c</sup>

<sup>a</sup> Institute for Solid State Electronics, Vienna University of Technology, Austria

<sup>b</sup> Atmel Germany GmbH Theresienstraße 2, 74025 Heilbronn, Germany

<sup>c</sup> FH Osnabrück, FB Elektrotechnik, Albrechtstraße 30, 49076 Osnabrück, Germany

11:45 A laser-based instrument for measuring strain in electronic packages using coherent fibre-bundles

Peter Dias-Lalcaca<sup>a</sup>, Erwin Hack<sup>a</sup>, Filippo Visintainer<sup>b</sup>, Stefano Bernard<sup>b</sup>, Urs Sennhauser<sup>a</sup>

<sup>a</sup> Swiss Federal Laboratories for Materials Testing and Research (EMPA), Electronics / Metrology Lab, Switzerland

b Centro Ricerche Fiat, CRF, Italy

12:10 Localization of FET Device Performance with Thermal Laser Stimulation

Sanjib K. Brahma<sup>a</sup>, Christian Boit<sup>a</sup>, Arkadiusz Glowacki<sup>a</sup>, H. Suzuki<sup>b</sup>

<sup>a</sup> Berlin University of Technology, Einsteinufer 19, Sekr. E2, D-10587 Berlin, Germany

b Hamamatsu Photonics K.K., Japan

## Session Device, Circuit & MEMs Reliability (DCM)

Room D 7.2

Chair: Y. Danto, University of Bordeaux

10:55 Degradation of electrical performance and floating body effect in ultra thin gate oxide FD-SOI n-MOSFETs by 7.5-MeV proton irradiation

K. Hayama<sup>a</sup>, K. Takakura<sup>a</sup>, H. Ohyama<sup>a</sup>, A. Mercha<sup>b</sup>, E. Simoen<sup>b</sup>, C. Claeys<sup>bc</sup>, J.M. Rafi<sup>d</sup> and M. Kokkoris<sup>e</sup>

a Kumamoto National College of Technology, Japan

b IMEC Leuven. Belgium

<sup>c</sup> Electrical EEngineering Department, KU Leuven, Belgium

d Institut de Microelectrònica de Barcelona (CNM-CSIC), Spain

<sup>e</sup> Institute of Nuclear Physics, Tandem Accelerator, Greece

11:20 Reliability Evaluation and Redesign of LNA

Wei-Cheng Lin, Long-Jei Du, Ya-Chin King

Microelectronics Laboratory, Semiconductor Technology Application Research (STAR)

Group, Department of Electrical Engineering, National Tsing-Hua University, Taiwan

11:45 Creep as a reliability problem in MEMS

R. Modlinski<sup>ab</sup>, A. Witvrouw<sup>a</sup>, P. Ratchev<sup>a</sup>, A. Jourdain<sup>a</sup>, V. Simons<sup>a</sup>, H.A.C. Tilmans<sup>a</sup>, J.M.J. den Toonder<sup>C</sup>. R. Puers2<sup>b</sup> and I. De Wolf<sup>a</sup>

<sup>a</sup> IMEC vzw. Belgium

<sup>b</sup> E. E. Dept of K. U. Leuven, Belgium,

<sup>c</sup> Philips Research Laboratories. The Netherlands

12:10 Impact of the space environmental conditions on the reliability of a MEMS COTS based system

P. Schmitt<sup>ab</sup>, X. Lafontan<sup>c</sup>, F. Pressecq<sup>a</sup>, B. Kurz<sup>a</sup>, C. Oudea<sup>d</sup>, D. Estève<sup>b</sup>,

J.Y. Fourniols<sup>b</sup>. H. Camon<sup>b</sup>

<sup>a</sup> CNES, bpi 1414, 18, Av. E. Belin, 31401 Toulouse Cedex 9, France

b LAAS - CNRS, 7, Av. Col. Roche, 31077 Toulouse Cedex 4, France

<sup>c</sup> Nova MEMS, 14 rue du quai, 09700 Saverdun, France

d EADS – ST, 66, route de Verneuil, 78133 Les Mureaux Cedex, France

#### Lunch

13:30 Departure for Networking Event and Gala Dinner

Meeting Point: ETH Terrace (Side Leonhardstrasse)

Session ESD (ESD) Auditorium Maximum

Chair: T. Mouthaan. University of Twente

8:45 Experimental measurements and 3D simulation of the parasitic lateral bipolar transistor triggering within a single finger gg-nMOS under ESD

P.Galya, V.Berlandab, A.Guilhaumec, F.Blancd, J.P.Chantee

<sup>a</sup> Pole Universitaire Leonard de Vinci, France

b LORE, France

<sup>c</sup> EADS CCR, Centre Commun de Recherche, France

<sup>d</sup> PHILIPS Semiconductor, France

e CEGELY INSA Lyon, France

Low Frequency Noise Measurements for ESD Latent Defect Detection in High Reliability 9:10 **Applications**

N. Guitard<sup>a</sup>, D. Trémouilles<sup>a</sup>, M. Bafleur<sup>a</sup>, L. Escotte<sup>a</sup>, L. Bary<sup>a</sup>, P Perdu<sup>b</sup>,

G. Sarrabayrouse<sup>a</sup>, N. Nolhier<sup>a</sup>, R. Reyna-Rojas<sup>b</sup>

<sup>a</sup> LAAS/CNRS, France

<sup>b</sup> CNES, France

9:35 Electrostatic Effects on Semiconductor Tools

P. Jacobab. J. C. Reinera

<sup>a</sup> EMPA Swiss Federal Laboratories for Materials Testing and Research, Switzerland

<sup>b</sup> EM Microelectronic Marin SA, Rue des Sors 2-3, CH-2074 Marin, Switzerland

10:00 Multiple-time-instant 2D thermal mapping during a single ESD event

V. Dubec<sup>a</sup>, S. Bychikhin<sup>a</sup>, M. Blaho<sup>a</sup>, M. Heer<sup>a</sup>, D. Poganya<sup>a</sup>, M. Denison<sup>b</sup>. N. Jensen<sup>b</sup>. M. Stecher<sup>b</sup>, G. Groos<sup>c</sup>, E. Gornik<sup>a</sup>

<sup>a</sup> Institute for Solid State Electronics, Vienna University of Technology, Austria

b Infineon Technologies, Germany

<sup>c</sup> University of the Federal Armed Forces Munich, Germany

# Session Interconnects Reliability (INT)

Room D 7 2

Chair: F. Fantini, University of Modena

- 8:30 Reliability Challenges with Ultra-Low k Interlevel Dielectrics (INVITED) J.R. Lloyd, M.R. Lane, X.-H. Liu, E. Liniger, T.M. Shaw, C.-K. Hu, R. Rosenberg IBM T.J. Watson Research Center, Yorktown Heights NY 10598, USA

- 9.10 Reliability Improvement in Al Metallization: A Combination of Statistical Prediction and Failure Analytical Methodology

G. Zhang<sup>a</sup>, C. M. Tan<sup>a</sup>, K. T. Tan<sup>b</sup>, K. Y. Sim<sup>b</sup>, and W. Y. Zhang<sup>b</sup>

<sup>a</sup> Division of Microelectronics, School of EEE, Nanyang Technological University, Singapore <sup>b</sup> Department of Failure Analysis & Reliability, Systems on Silicon Manufacturing Co., Singapore

MTF test system with AC based dynamic joule correction for electromigration tests on

9:35 interconnects

L. Biesemans<sup>ac</sup>, K. Schepers<sup>a</sup>, K. Vanstreels<sup>a</sup>, J. D'Haen<sup>b</sup>, W. De Ceuninck<sup>ab</sup>, M. D'Olieslaeger<sup>ab</sup> <sup>a</sup> Institute for Materials Research, Limburgs Universitair Centrum, Belgium

b IMEC vzw, division IMOMEC, Wetenschapspark 1, B-3590 Diepenbeek, Belgium

<sup>c</sup> Hogeschool Limburg, Universitaire Campus, Gebouw H, B-3590 Diepenbeek, Belgium

10:00 An improved isothermal electromigration test for Cu-damascene characterization M. Impronta<sup>a</sup>, S. Farris<sup>a</sup>, A. Scorzoni<sup>ab</sup>

<sup>a</sup> Istituto per la Microelettronica e Microsistemi (CNR-IMM), Consiglio Nazionale delle Ricerche, Italy

<sup>b</sup> Dipartimento di Ingegneria Elettronica e dell'Informazione, Università di Perugia, Italy

#### Session TCAD for Reliability (TCAD)

Auditorium Maximum

Co-chairs: L. Bomholt, ISE AG, M. Stecher, Infineon

10:55 Analysis of the layout impact on electric fields in interconnect structures using finite element method

Changsoo Honga, Linda Milora, MZ Linb

<sup>a</sup> School of Electrical and Computer Engineering, Georgia Institute of Technology, USA

<sup>b</sup> Taiwan Semiconductor Manufacturing Company, Ltd., Hsin-Chu, Taiwan, R.O.C.

11:20 Characterization of self-heating effects in semiconductor resistors during transmission line pulses.

C. Corvasce<sup>a</sup>, M. Ciappa<sup>a</sup>, D. Barlini<sup>a</sup>, S. Sponton<sup>b</sup>, G. Meneghesso<sup>b</sup>, W. Fichtner<sup>a</sup>

<sup>a</sup> Swiss Federal Institute of Technology (ETH) Zurich, Integrated Systems Laboratory, Switzerland

<sup>b</sup> University of Padova, Department of Information Engineering, Italy

11:45 Statistical simulation of gate dielectric wearout, leakage, and breakdown

A. Gehring and S. Selberherr

Institute for Microelectronics, Vienna University of Technology, Austria

12:10 A CAD assisted design and optimisation methodology for over-voltage ESD protection circuits

V.Vassilev<sup>ab</sup>, V.Vashchenko<sup>c</sup>, Ph.Jansen<sup>a</sup>, B.-J. Choi<sup>c</sup>, A.Concannon<sup>c</sup>, J.-J.Yang<sup>c</sup>,

G.Groeseneken<sup>ab</sup>, M.I.Natarajan<sup>a</sup>, M.Terbeek<sup>c</sup>, P. Hopper<sup>c</sup>, M.Steyaert<sup>b</sup>, H.E.Maes<sup>ab</sup>

<sup>a</sup> IMEC Leuven, Belgium

b KUL, ESAT, Belgium

<sup>C</sup> National Semiconductor Corp., USA

12:35 Closing and BP Award

# Registration

Registration either on-line ( http://www.iis.ee.ethz.ch ) or at the desk.

Administrative secretary of the conference:

Christine Haller

Swiss Federal Institute of Technology (ETH)

Integrated Systems Laboratory

ETH-Zentrum

CH-8092 Zurich, Switzerland

Phone +41 1 632 4268 Fax +41 1 632 1194

Email esref04@iis.ee.ethz.ch

# Desk location and opening hours

The registration desk is located at the Floor F of the ETH Main Building at the Rämistrasse 101, CH-8092 Zurich. The opening hours of the desk are

Monday, October 4

10:00

- 19:00

Tuesday, October 5

08:00

- 19:00

Wednesday, October 6

08:30

- 19:00

Thursday, October 7

08:30

- 13:30

Friday, October 8

08:30

- 13:00

See the conference homepage for the phone numbers and the email addresses to reach the delegates.

# Main Building ETH

#### Workshops

The access to the workshops is included in the fees.

# **Best Paper Award Exchange Program**

Chair: W. Wondrak, Daimler Chrysler

The recipient of the Best Paper Award will be entitled to present his/her paper either at the International Reliability Physics Symposium (IRPS, USA), or at the Reliability Center of Japan Symposium (RCJ, Japan), or at the International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA, Singapore) as an invited paper. The ESREF organization covers 1000 Euro for the travelling expenses.

#### **Equipment Exhibition**

The access to the equipment exhibition is included in the fees.

#### Lunch and coffee breaks

The lunches and the coffee breaks mentioned in the Conference schedule are included in the fees

Lunches will be served before 13:30 in the ETH Mensa (lunch restaurant), which is located within the ETH Main building (side Leonhardstrasse, see map), while coffee breaks will be served in the exhibition area.

# Reception party, networking event and gala dinner

The tickets for the reception party, networking event, and for the gala dinner are included in the fees.

The reception party takes place in conjunction with the Poster session in the patio at the Floor F of the ETH Main Building starting at 18:00.

A limited amount of tickets for the networking event and for the gala dinner are also available for companions. Please contact the registration desk before Tuesday Oct. 5, 12:00 to check for price and availability. The meeting point for the networking event and gala dinner is the ETH Terrace (side Leonhardstrasse, see map) at 13:30. Retour to Zurich is planned for 24:00.

#### Internet access for the delegates

Internet accesses will be available on the conference site for the delegates (room F 33.3).

# Author preparation room

Computers are available in the author preparation room (F 33.3) to apply minor corrections to the electronic presentations. All presentations have to be finalized and approved by the audiovisual officer either the evening before the session (for sessions in the morning of the next day), or not later than 3 hours before the beginning of the session (for sessions in the afternoon).