Eindhoven University of Technology Virtual Reliability Qualification Prof. Kouchi (G.Q.) Zhang g.q.zhang@philips.com g.q.zhang@tue.nl

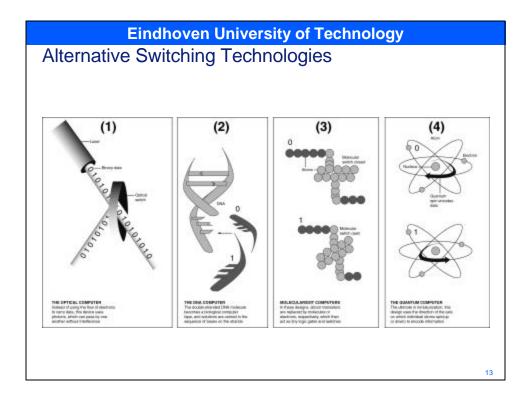

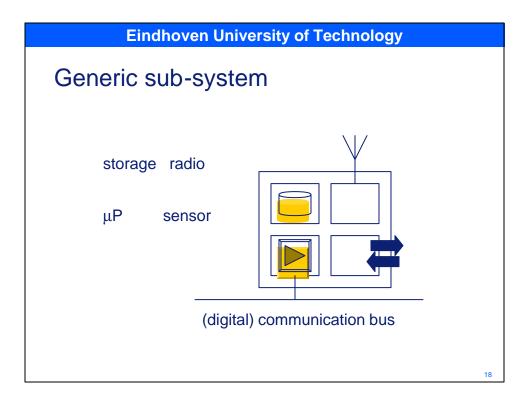

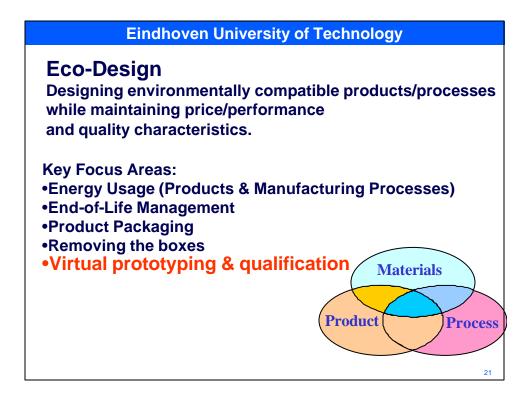

- Moving from a world of electronic "boxes" to the world of ambient intelligence where technology is built into our environment via connectivity and integration.

- Focus on function, not the devices that enable them.

sensitive to people's needs

personalized to their requirements

anticipatory of their behavior and

responsive to their presence

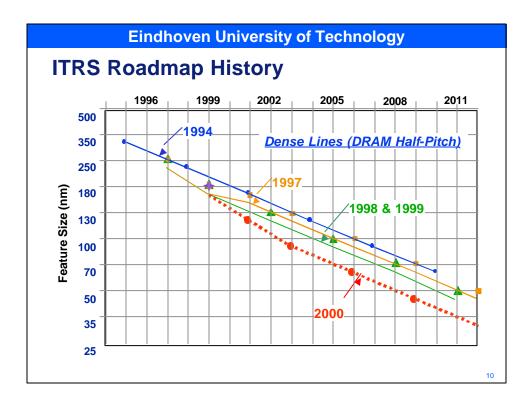

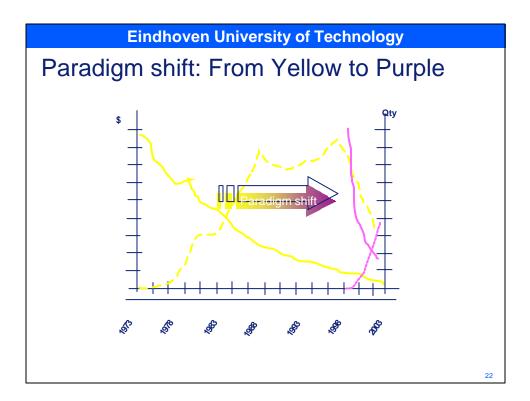

Process technology evolution System-on-Chip: standardization

- Standard CMOS density will continue to grow exponentially, driving down the cost of digital data processing and storage

- More Moore : System-on-Chip

- But realized digital design complexity increasingly lags behind the potential of new technologies, while investments soar

- Decelerating long-term semiconductor market growth to single digit

Let's see some famous forecasts

"I think there is a world market for maybe five computers " *Thomas Watson, Chairman of IBM, 1943*

"Computers in the future may weigh no more than 1.5 tons" Popular Mechanics Magazine, 1949

" 640K ought to be enough for anybody " Bill Gates, 1981

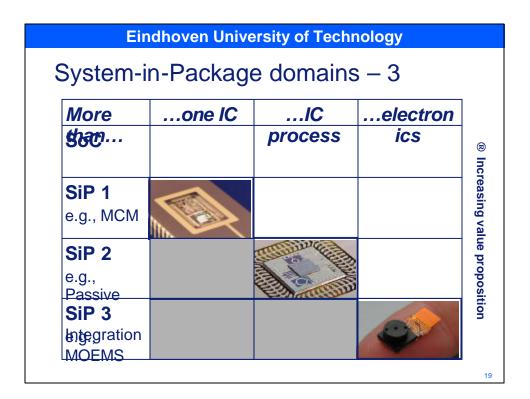

| Eindhoven University of Technology                                                                                                                                                                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| More Moore and more than moore<br>Complementing, not competing                                                                                                                                                                                                |  |

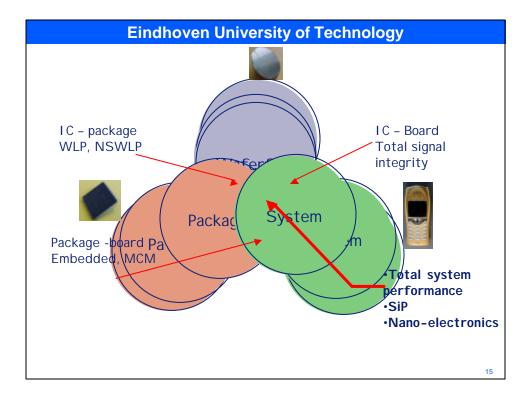

| <ul> <li>More Moore: SoC- Programmable monolithic IC</li> <li>Advanced baseline CMOS, standard packaging</li> <li>Maximize utilization of (expensive) mask sets</li> <li>Diversification is in the software &amp; embedded IP mix</li> </ul>                  |  |

| <ul> <li>More than Moore: SiP - Multi-technology module</li> <li>Mature and advanced wafer processes, advanced packaging</li> <li>Maximize utilization of dedicated option fabs</li> <li>Diversification is in the components &amp; technology mix</li> </ul> |  |

|                                                                                                                                                                                                                                                               |  |

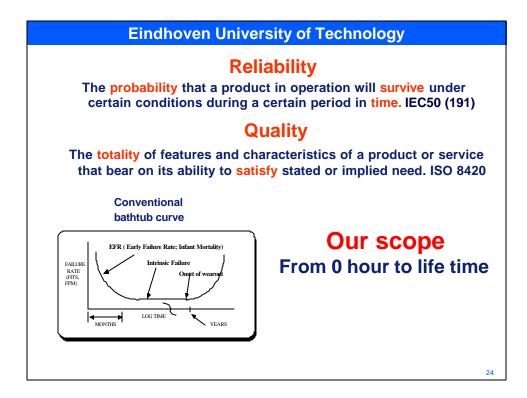

# 2. Consequences for reliability

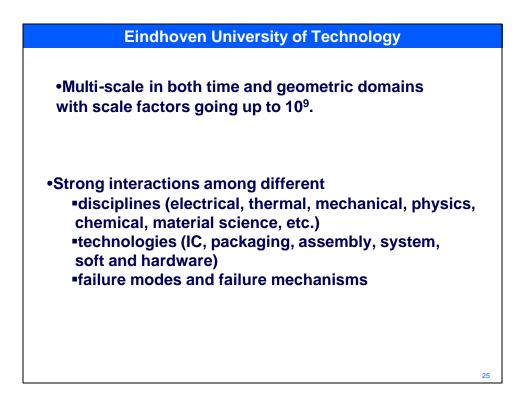

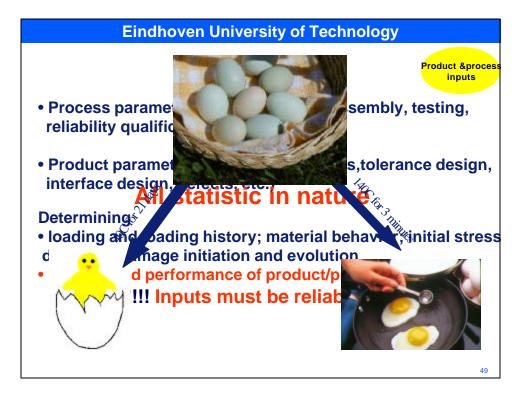

•Behaviour is strongly non-linear, stochastic, time and temperature dependence.

•Greatly increased loading intensity/loading steps

•Greatly increased design complexity and shrinking of design margin to nano levels.

•Strict demand on and challenges for ensuring quality, robustness and reliability to cover the total value chain

$\mathbf{Q\&R} = \mathbf{???} f_1(\mathbf{b}_1, \mathbf{b}_2, \dots \mathbf{b}_i) f_2(\mathbf{c}_1, \mathbf{c}_2, \dots \mathbf{c}_i) f_3(\mathbf{t}_1, \mathbf{t}_2, \dots \mathbf{t}_i) d\mathbf{b} d\mathbf{c} d\mathbf{t}$

b: Business variables c: Consumer variables t: Technical variables

f<sub>3</sub>(t<sub>1</sub>, t<sub>2</sub>,.. t<sub>i</sub>..)= **??F**<sub>1</sub>(material) F<sub>2</sub>(process) F<sub>3</sub>(product)

**Q&R** is innovation and integration of innovations

| Eindhoven University of Technology                        |   |

|-----------------------------------------------------------|---|

| Wear out                                                  |   |

| - Fatigues                                                |   |

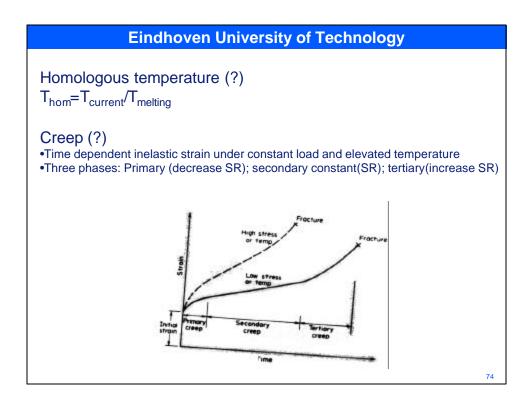

| - Creep                                                   |   |

| - Wear                                                    |   |

|                                                           |   |

| Overstress                                                |   |

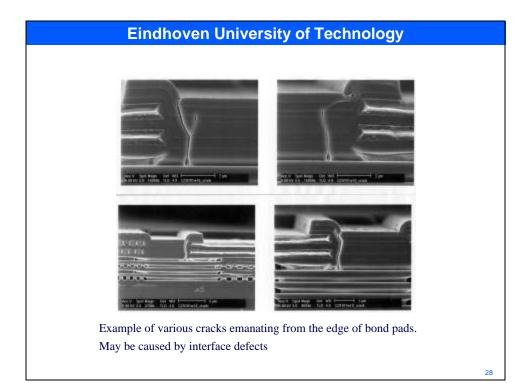

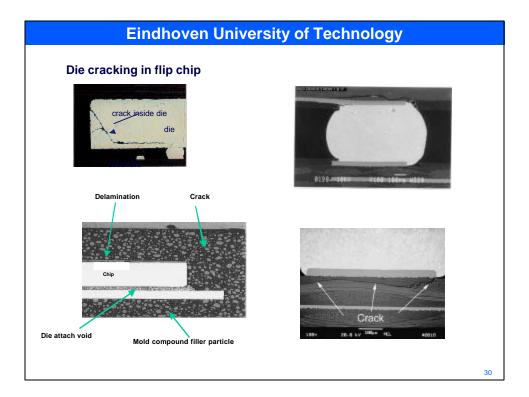

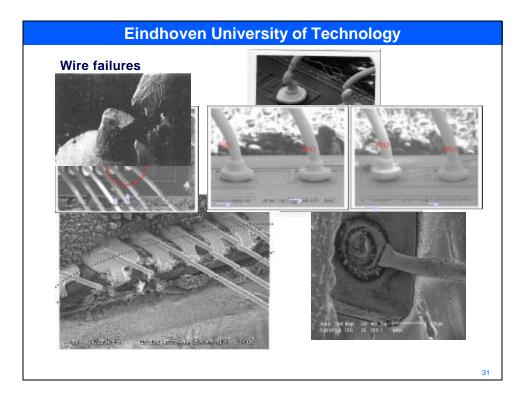

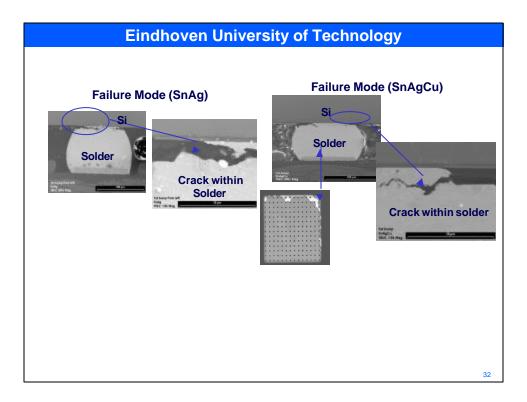

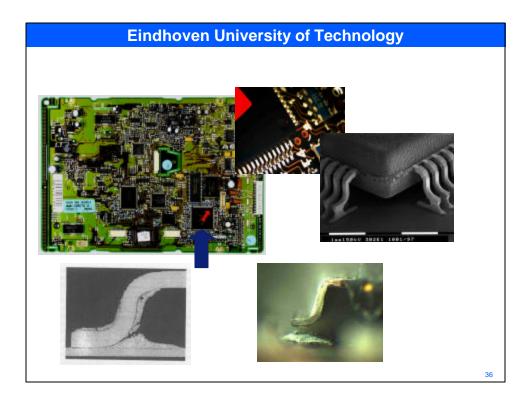

| <ul> <li>Cracks (die, plastic, wirebond, etc.)</li> </ul> |   |

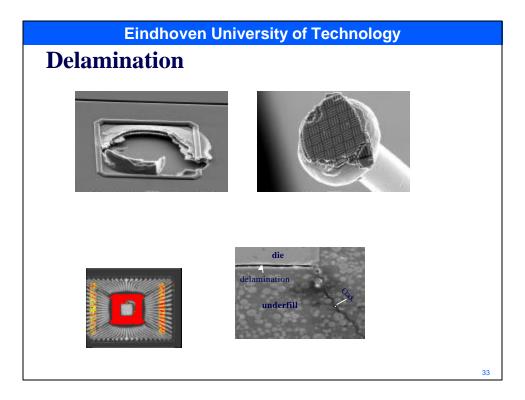

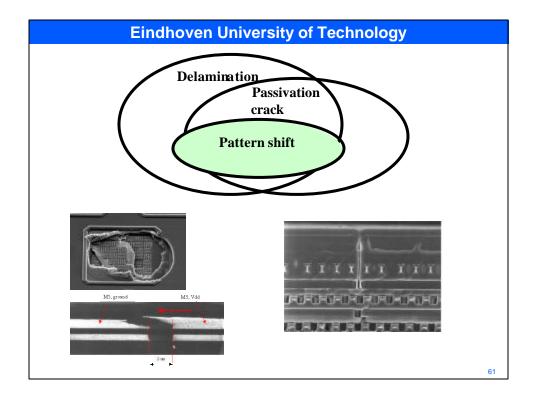

| - Delamination                                            |   |

| - Pop-corn                                                |   |

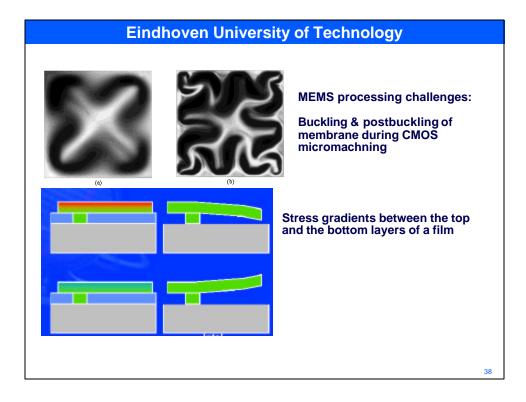

| - Buckling                                                |   |

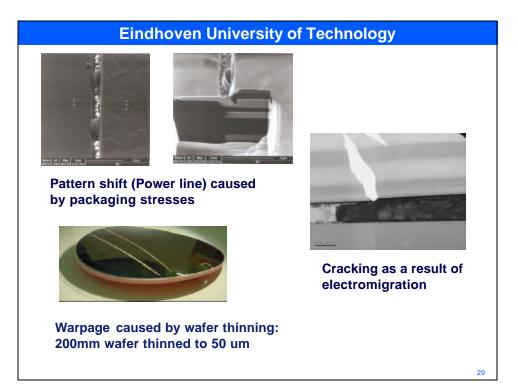

| - Yields (ball shear, pattern shift, etc.)                |   |

| - Warpage                                                 |   |

| - Large deformation                                       |   |

| - Electro/thermal/stress migration                        |   |

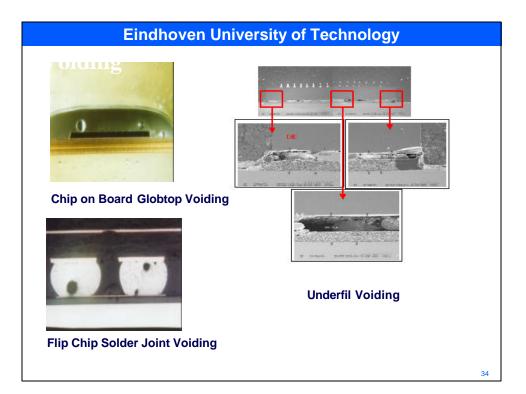

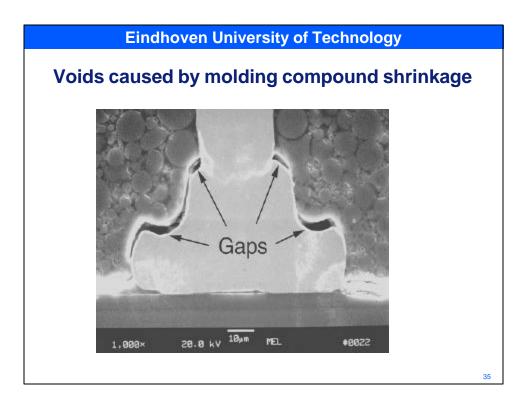

| - Voiding                                                 |   |

|                                                           |   |

|                                                           | 4 |

Eindhoven University of Technology

New and combined failure modes &mechanisms

>65% of failures thermo-mechanical related!

# **Eindhoven University of Technology**

### No appropriate thermo-mechanical design method

- •Experience and trial-error based design method

- •Empirical, phenomenological, case dependent,

- •Sub-optimal product/process

- •High development costs

# No appropriate thermo-mechanical qualification method

- •Time and money consuming

- •Unclear correlation between application profiles with spec. and accelerated testing

- •No guarantee for extrapolating to outside of the spec.

- •No satisfied coverage for quality, robustness and reliability

41

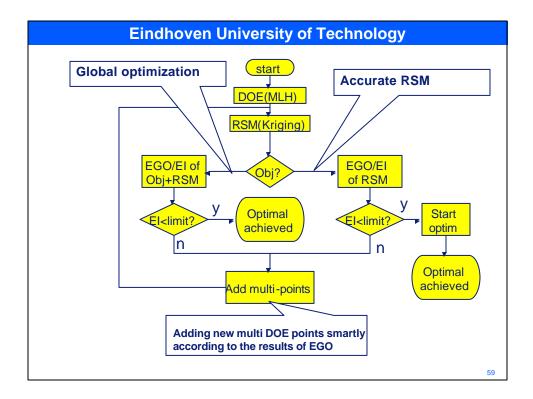

#### **Eindhoven University of Technology** Problem Expensive for nonlinear responses Objective To develop smart infill sampling strategy & criteria for efficient and reliable RSM development and global optimization Method EGO (Efficient Global Optimization): Expected Improvement (low objective function in optimal objective region & high uncertainty in larger error region) (a) (b) 0.01 0.06 12 12 0.009 0.05 10-10-800.0 0.007 0.04 8 8 0.006 6 0.03 6 0.005 0.004 4 0.02 4 0.003 0.002 2-0.01 2 0.001 0 0 슝 0 2 10 12 6 12 6 8 2 4 8 10 58

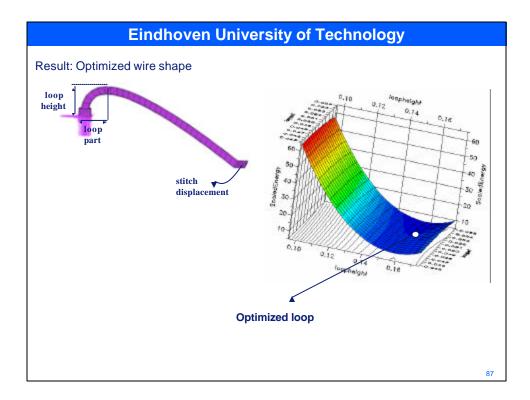

# Example: Optimizing wire loop design to prevent wire break

### Problem:

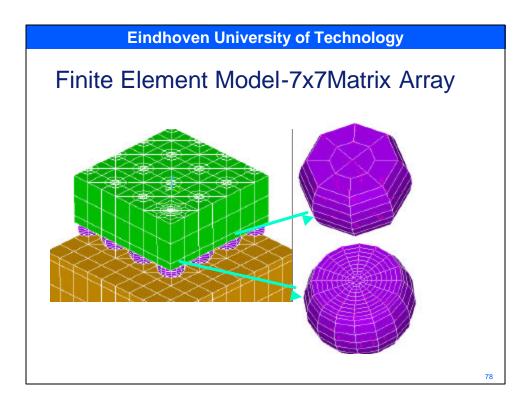

Interconnect wire break is the dominant failure in electronic packaging. Figs. 1 & 2 show the failure on the stitch and the ball side, respectively. There is urgent industrial need to design optimal wire loop in order to prevent possible wire breaks.

### Method:

Due to the large scale difference, global-local method is used in developing reliable FEM models to simulate the stress levels in a wire, in combination with nonlinear material model of the wire. From the global package model, wire deformations are obtained and serve as the input for the local wire model.

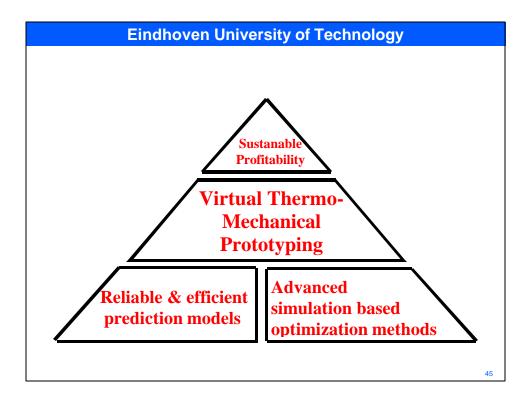

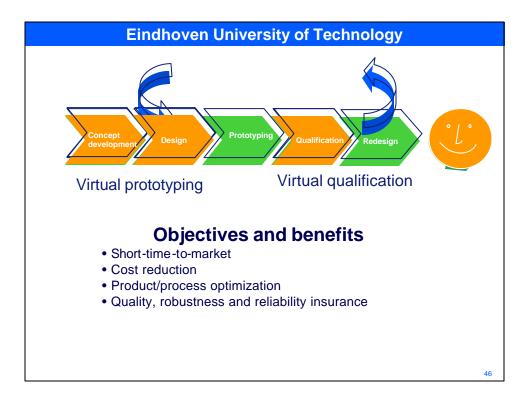

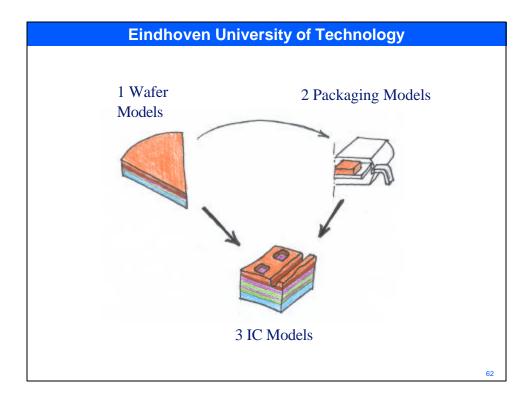

- Future technology/business development trends demand virtual prototyping/virtual qualifications.

- The developed methodologies can generate high added business values.

- Not to replay physical prototyping/qualification, but to reduce their numbers and duration.

- Many challenges remain. Combined effort needed.