# Journal of Analog Innovation

October 2011

Volume 21 Number 3

#### IN THIS ISSUE

2-channel and 4-channel pin-selectable I<sup>2</sup>C multiplexer 11

high efficiency power supply for Intel IMVP-6/6+/6.5 CPUs 20

3A linear regulator easily paralleled to spread power and heat 24

LTspice IV update 36

frequency shifter for isolated PWM control 40

## Fast, Accurate Step-Down DC/DC Controller Converts 24V Directly to 1.8V at 2MHz

**Bud Abesingha**

The continuous march in electronics toward lower supply voltages and higher load currents puts tremendous pressure on point-ofload DC/DC converters to maintain a fast pace of performance improvements. For instance, a lower supply voltage means a regulator must support a higher step-down ratio from a 12V or 24V power rail while maintaining high efficiency. Regulation accuracy also becomes more important as supply voltages

drop—and accuracy must be maintained in the presence of parasitic IR drops and dynamic load transients. EMI generated by switching converters is also of concern, especially in RF applications.

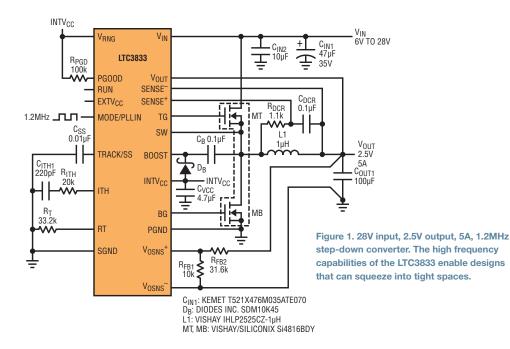

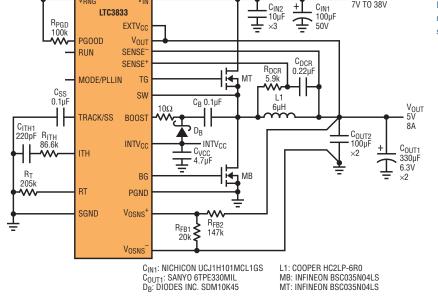

Some applications require that their power supplies meet all of these stringent requirements: high power, high efficiency, high accuracy, high stepdown ratio, fast transient performance and low EMI—and that they do it in a small footprint. The LTC<sup>®</sup>3833 is a high performance synchronous step-down DC/DC controller that steps up to the challenge. Figure 1 shows a typical application. The LTC3833 accepts an unregulated input voltage between 4.5v and 38v (40v abs max) and downconverts it to 0.67% accurate output voltage between 0.6v and 5.5v (6v abs max).

It features a 20ns minimum on-time, enabling a high step-down ratio (high  $v_{IN}$  to low  $v_{OUT}$ ) at high frequency (up to 2MHz), and its control architecture is primed for fast transient performance. The LTC3833 is offered in 20-pin QFN (3mm × 4mm) and TSSOP packages with exposed pads for enhanced thermal performance.

(continued on page 4)

Published September 2011 and now available. See page 2.

# Linear in the News

## In this issue.

#### **COVER STORY**

Fast, Accurate Step-Down DC/DC Controller Converts 24V Directly to 1.8V at 2MHz Bud Abesingha

#### **DESIGN FEATURES**

| 2-Channel and 4-Channel Pin-Selectable I <sup>2</sup> C<br>Multiplexer Features High Noise Margin, Capacitance<br>Buffering, Level Translation and Stuck Bus Recovery<br><b>Rajesh Venugopal</b>             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Low I <sub>q</sub> , High Efficiency Dual Output Controllers for<br>Wide Ranging Input and Output Voltages<br><b>Jason Leonard</b>                                                                           |  |

| High Efficiency Power Supply for Intel<br>MVP-6/IMVP-6+/IMVP-6.5 CPUs<br><b>Jian Li and Gina Le</b>                                                                                                          |  |

| 3A Linear Regulator Can Be Easily Paralleled to<br>Spread Power and Heat<br><b>Todd Owen</b>                                                                                                                 |  |

| 8-Output Regulator Powers Applications Processors<br>Kevin Ohlson                                                                                                                                            |  |

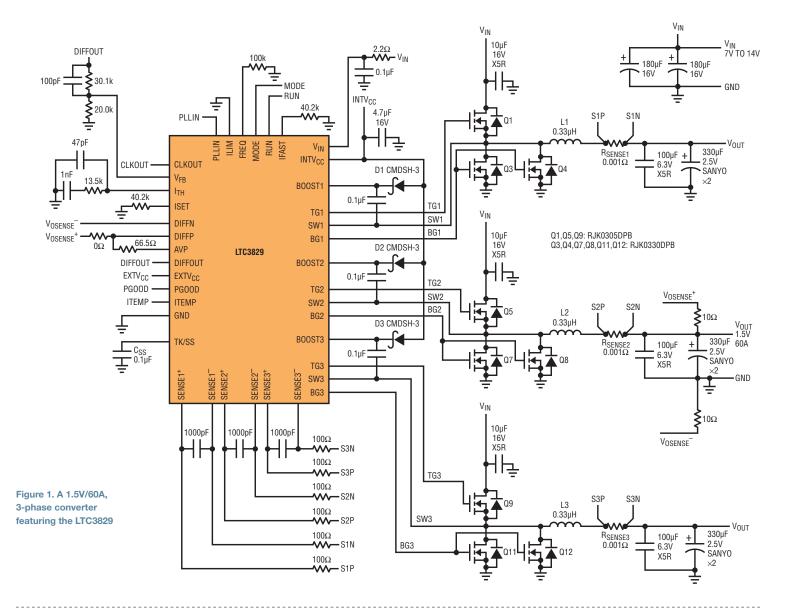

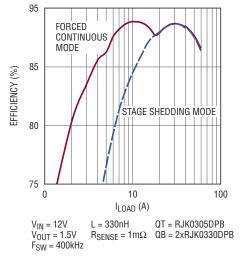

| 3-Phase Synchronous Step-Down DC/DC<br>Controller with Stage Shedding™, Active Voltage<br>Positioning and Nonlinear Control for High<br>Efficiency and Fast Transient Response<br>Jian Li and Kerry Holliday |  |

| DESIGN IDEAS                                                                                                                                                                                                 |  |

| What's New with LTspice <sup>®</sup> IV?<br>Gabino Alonso                                                                                                                                                    |  |

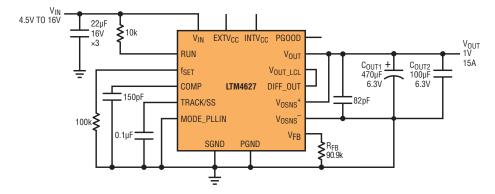

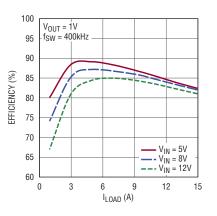

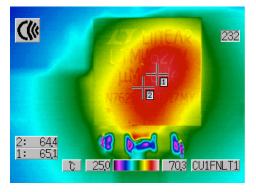

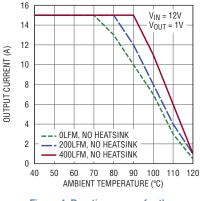

| 15A µModule <sup>®</sup> Regulator Solves Thermal Problems<br>by Converting 12V to 1V with High Efficiency<br>Eddie Beville                                                                                  |  |

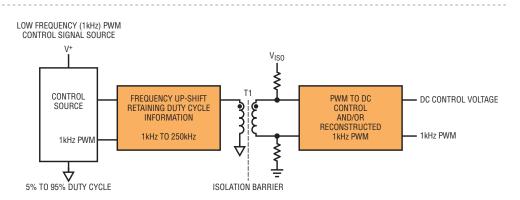

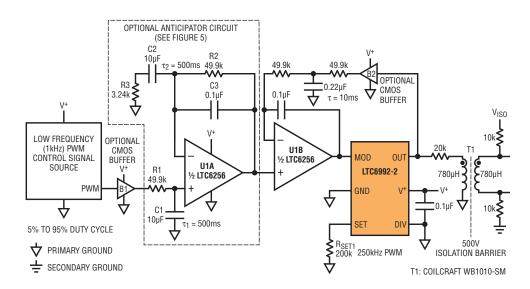

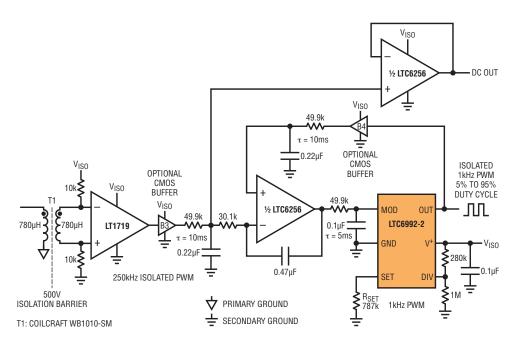

| Solve Isolated Control Problems by Up-Shifting<br>Control Frequency with TimerBlox <sup>®</sup> PWM Generator<br><b>Tim Regan</b>                                                                            |  |

| product briefs                                                                                                                                                                                               |  |

| back page circuits                                                                                                                                                                                           |  |

|                                                                                                                                                                                                              |  |

#### ANALOG CIRCUIT DESIGN BOOK PUBLISHED

The much-anticipated book, *Analog Circuit Design: A Tutorial Guide to Applications and Solutions* was just published by Newnes, an imprint of Elsevier Science & Technology Books. Edited by industry gurus, Bob Dobkin and Jim Williams, the 960-page book covers a broad range of analog design topics. This is the first time that such an extensive collection of application notes has appeared in one volume from Linear Technology engineers.

Analog Circuit Design is a comprehensive source book of circuit design solutions that will aid systems designers with elegant and practical design techniques that focus on common circuit design challenges.

The book includes an extensive power management section, covering such topics as switching regulator design, linear regulator design, high voltage and high current applications, powering lasers and illumination devices, and automotive and industrial power design. Other sections of the book span a broad range of analog design areas, including data conversion, signal conditioning and high frequency/RF design.

Jim Williams wrote in the book's Introduction, "The nature of analog circuit design is so diverse, the devices so sophisticated, and user requirements so demanding that designers require (or at least welcome) assistance. Ultimately, the use of analog ICs is tied to the user's ability to solve the problems confronting them. Anything that enhances this ability, in both specific and general cases, obviously benefits all concerned."

Bob Dobkin stated in the book's Foreword, "One of the best avenues for learning analog design is to use the application notes and information from companies who supply analog integrated circuits. These application notes include circuitry, test results, and the basic reasoning for some of the choices made in the design of these analog circuits. They provide a good starting point for new designs.

"Since the applications are aimed at solving problems, the application notes, combined with the capability to simulate circuits on Spice, provide a key learning pathway for engineers. The analog information in most of these application notes is timeless and will be as valid twenty years from now as it is today. It's my hope that anyone reading this book is helped through the science and art of good analog design."

For more information, go to www.linear.com/designtools/acd\_book.php. To purchase *Analog Circuit Design*, click on the Elsevier link for a 30 percent discount on the cover price, or go to the Amazon link at the bottom of the page. Jim Williams' workbench

#### COMPUTER HISTORY MUSEUM EXHIBIT ON ANALOG & JIM WILLIAMS OPENS The Computer History Museum

in Mountain View, California has announced a new exhibit opening this month, "An Analog Life: Remembering Jim Williams." The exhibit, which

runs from October 15, 2011 until April 15, 2012, will focus on how engineers work.

In their project overview for the exhibit, the museum's curator stated, "It is said that we spend about one-third of our lives at work. How we work is often reflected in the way we organize our desks and workspaces. Analog circuit guru Jim Williams' workbench tells us some things about the way he worked. For example, with its years-old strata of past circuits embedded in a matrix of thousands of overlapping components and still more circuits, we see someone who worked iteratively, drawing on past designs to continually invent new circuits and systems.

"Jim Williams' workbench is an inspirational object that allows Computer History Museum visitors to explore engineering work styles, be inspired by an extraordinary person and discover the world of analog circuitry and its impact on today's technology."

The centerpiece of the exhibit is Jim Williams' engineering workbench, which

the museum carefully transported from his Linear Technology lab to the museum. The display will include interpretive graphics, explaining various aspects of analog design. In addition, the exhibit includes video interviews with engineers who worked closely with Jim Williams over the years, plus video footage of his labs, both at Linear Technology and at his home lab.

The "Analog Life" exhibit will launch on October 15, with an evening event at the Computer History Museum. Visitors to the launch will have an opportunity to view the exhibit, hear a panel discussion of analog experts discussing analog design and Jim Williams' contributions, and attend a book signing of the new *Analog Circuit Design* book with co-editor Bob Dobkin. For more information about the exhibit, visit computerhistory.org/highlights/analoglife. **30 YEARS OF ANALOG INNOVATION** On September 26, Linear Technology commemorated three decades of innovation in analog integrated circuits. When the company was founded in September 1981,

at the dawn of the digital revolution, some questioned the wisdom of founding a company focused purely on analog technology. Since then, the analog

market has grown 20-fold with Linear contributing solutions to all corners of the electronics industry. The dawn of digital only *increased* the demand for analog.

Linear is consistently at the leading edge of new electronic markets as they have emerged. These include the PC revolution, laptop and tablet computers, industrial control and robotics, network infrastructure, cellular and satellite communications, automotive electronics including advanced displays, electronic braking and steering and now the growth of the hybrid/electric automotive segment, to name just a few.

A video interview with Linear Technology co-founders Bob Swanson and Bob Dobkin and CEO Lothar Maier can be found at www.linear.com/30yearinterview.

# The LTC3833 is a high performance synchronous step-down DC/DC controller that regulates to 0.67% output accuracy, operates up to 2MHz switching frequency and has a 20ns minimum on-time.

#### (LTC3833, continued from page 1) FAST TRANSIENT PERFORMANCE AND CONSTANT FREQUENCY

The LTC3833 uses a new, sophisticated *controlled*-on-time architecture—a variant of the *constant* on-time control architecture with the distinction that the on-time is controlled so that the switching frequency remains constant over steady state conditions under line and load. This architecture takes advantage of all the benefits of a constant on-time controller, namely fast transient response and small on-times for high step-down ratios, while imitating the behaviors of a constant frequency controller.

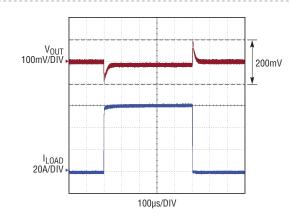

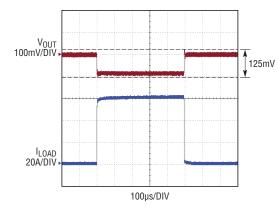

The LTC3833 can respond to a load step immediately without waiting until the next switching cycle as in a conventional constant frequency controller. During a load step, the LTC3833 increases its switching

| EFFICIENCY      |     | FREQUENCY, INDUCTANCE |                |              |              |  |

|-----------------|-----|-----------------------|----------------|--------------|--------------|--|

|                 |     | 200kHz, 2.00µH        | 500kHz, 0.82µH | 1MHz, 0.47µH | 2MHz, 0.20µH |  |

|                 | 6V  | 91%                   | 92%            | 91%          | 87%          |  |

| V               | 12V | 92%                   | 92%            | 89%          | 84%          |  |

| V <sub>IN</sub> | 15V | 92%                   | 91%            | 87%          | 81%          |  |

|                 | 24V | 91%                   | 88%            | 83%          | 73%          |  |

Table 1: Example of efficiency variation over input and frequency. Higher frequencies have lower efficiencies but allow smaller component size for compact solutions. V<sub>OUT</sub> = 1.8V I<sub>LOAD</sub> = 10A.

frequency to respond faster and reduce the droop on the output. Similarly, during a load release, the LTC3833 reduces the switching frequency in order to prevent the input rail from charging the output capacitor any further. Once the transient condition subsides, the LTC3833 brings the switching frequency back to the nominal programmed value, or to the external clock frequency if it is being synchronized.

The LTC3833's low minimum off-time of 90ns allows it to achieve high duty cycle operation and thus avoid output dropout when  $v_{IN}$  is only slightly above the required  $v_{OUT}$ . The low minimum off-time also factors into fast transient performance. If the switching converter's control loop is designed for high bandwidth and high speed, the minimum off-time of the LTC3833 does not limit performance. That is, in a load step condition, the time between consecutive on-time pulses can be as low as 90ns for a high bandwidth design.

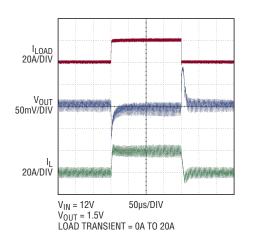

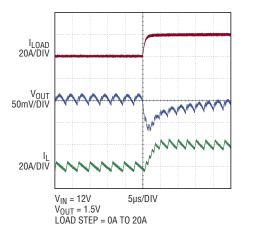

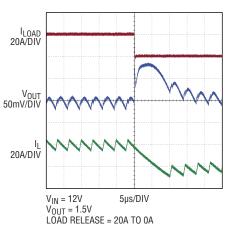

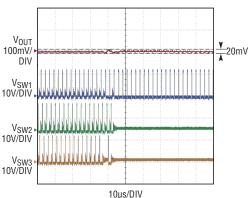

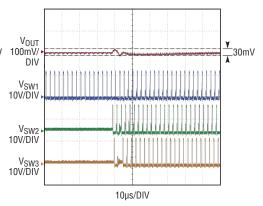

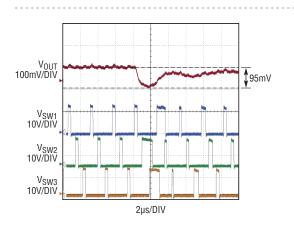

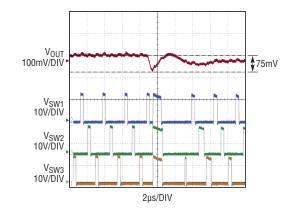

Figure 2 shows a low voltage, high current application typical of a microprocessor power supply where the LTC3833 responds quickly to a 20A load step and release.

#### WIDE FREQUENCY RANGE FOR A MULTITUDE OF APPLICATIONS The LTC3833 is capable of a full decade

of switching frequency, from 200kHz to 2MHz (programmed with an external resistor on the RT pin). This wide range allows the LTC3833 to meet the requirements of a wide variety of applications, from low frequency applications that require high efficiency, to higher frequency

INTV<sub>CC</sub> V<sub>IN</sub> 4.5V TO 14V VIN C<sub>IN1</sub> 180µF CIN2 + 2211 R<sub>PGD</sub> LTC3833 Ŧ Ξ Figure 2a. 14V input, 1.5V output, 20A, 300kHz step-down converter. The ×2 16V 100k LTC3833 excels in low voltage, high current applications such as these, PGOOD VOUT which are typical of a microprocessor power supply. It can respond quickly to sudden, high slew current requirements of the microprocessor. SENSE RUN SENSE МТ TC RNG R<sub>SENSE</sub> L1 MODE/PLLIN SW V<sub>OUT</sub> 1.5V 0.47uH  $1.5 \text{m}\Omega$ BOOST **EXTV<sub>CC</sub>** С<sub>ОUT2</sub> 100µF applications that require smaller solu- $\mathbf{\hat{s}}_{15k}^{R_{FB2}}$ 20A CR C<sub>SS</sub> 0.1µF 0.1µF ×2 tion size, to 2MHz applications that stay INTV<sub>C</sub> FRACK/SS INTVcc С<sub>ОUT</sub> 330µ CITH2 47pF above the AM radio band while being CVCC 2.5V 4.7 ×2 able to downconvert from a high input C<sub>ITH1</sub> 220pF BG MR RITH 84 rail and deliver high output current. ~~~ PGND R<sub>T</sub> 137k RT VOSNS The choice of operating frequency is a SGND VOSNS tradeoff between efficiency and compo-CIN1: SANYO 16SVP180M L1: PULSE PA0515.471NLT COUT1: SANYO 2R5TPE330M9 MB: RENESAS RJK0330DPB nent size. Lower frequencies are more CENTRAL CMDSH-3 MT: RENESAS BJK0305DPB efficient due to a reduction of switching-

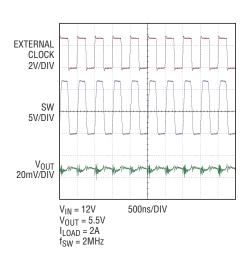

> The LTC3833's wide frequency range also helps minimize EMI interference from the switching regulator. The switching frequency can be chosen, and held over line and load, such that the operating frequency and harmonics of the regulator fall outside of the frequency band of the end application. This allows the end application to easily filter out switching noise of the DC/DC converter. Figure 3 shows an example of a 5.5v application that operates above the AM radio band (f<sub>SW</sub> > 1800kHz) that could be used to power electronics in an automotive infotainment system.

The LTC3833 provides an additional safeguard against EMI and noise interference by allowing it to be synchronized to an external clock applied to the MODE/PLLIN pin. This way, the end application has control over the DC/DC converter's switching cycles and timing so it does not interfere during critical time periods in the application where sensitive signal processing might occur.

#### Figure 2b. The LTC3833 can respond quickly to sudden, high slew current requirements.

related losses in the converter. On the

other hand, lower frequencies require

larger inductors and capacitors to achieve

a given output ripple. At higher frequen-

cies, smaller components can be used to

cost of efficiency. Table 1 illustrates the

trade-offs between efficiency and induc-

when the LTC3833 is used to generate a

1.8v output at several frequencies and

input voltages. As seen from the table,

switching losses are exacerbated at higher

frequencies and higher VIN, mainly due to

the higher  $v_{\mbox{\scriptsize DS}}$  across the high side mosfet.

tor size required to maintain output ripple

achieve the same output ripple, but at the

High  $V_{IN}$ , high frequency applications are susceptible to minimum on-time limitations. Consider converting 28V down to 2.5V at 1.2MHz: this requires an on-time of about 74ns, which the LTC3833 easily achieves.

#### HIGH STEP-DOWN RATIOS AT HIGH FREQUENCY

The LTC3833 supports high side MOSFET on-times down to 20ns. This is important as lower minimum on-times translate to higher possible step-down ratios ( $v_{IN}$  to  $v_{OUT}$ ) at a given switching frequency. Higher switching frequencies require lower on-times to achieve the same step-down ratio. Although the LTC3833's minimum on-time is a function of  $v_{IN}$ ,  $v_{OUT}$  and switching frequency (see the data sheet at www.linear.com/3833 for details), it scales in the correct direction—the lowest minimum on-time is at high  $v_{IN}$  to low  $v_{OUT}$  at high frequency.

Of course, high  $v_{IN}$ , high frequency applications are susceptible to minimum on-time limitations. Consider the application in Figure 1 that requires converting 28v down to 2.5v at 1.2MHz. This requires an on-time of about 74ns, which the LTC3833 easily achieves. In contrast, most conventional current mode controllers cannot achieve 74ns of on-time. To run at high frequency, a conventional current mode controller would require two stages of DC/DC conversion, with stage one converting down to an intermediate voltage rail (e.g. 12v), and stage two converting to the final required voltage. This effectively doubles the solution size and degrades overall efficiency.

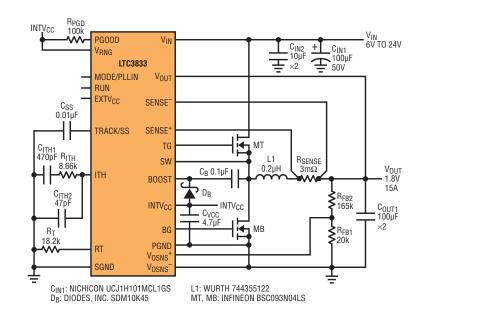

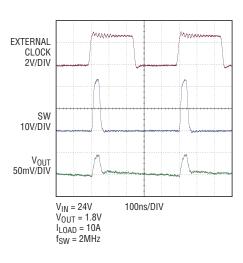

At very low on-times (20ns–60ns), the power MOSFETS' own switching delays can limit the minimum achievable on-time. Appropriate care must be given to choose power MOSFETS that have low turn-on and turn-off delays, and more importantly, little or no imbalance between their turn-on and turn-off delays. For example, most power MOSFETS' turn-off delay is about 30ns greater than their turn-on delay. This difference directly adds to the LTC3833's 20ns minimum on-time for an effective minimum on-time of about 50ns. Figure 4 shows a high step down ratio application operating at 2MHz where the high side power MOSFET has about a 12ns imbalance between turn-on and turn-off delays.

#### HIGH ACCURACY WITH MINIMAL EFFORT

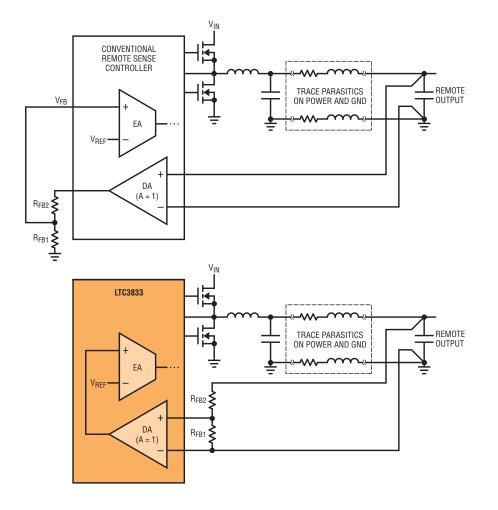

The LTC3833 features true remote differential output sensing. This enables accurate regulation of the output even in high power distributed systems with heavy load currents and shared ground planes. Remote differential sensing is critical for low output voltages, where small offsets caused by parasitic IR drops in

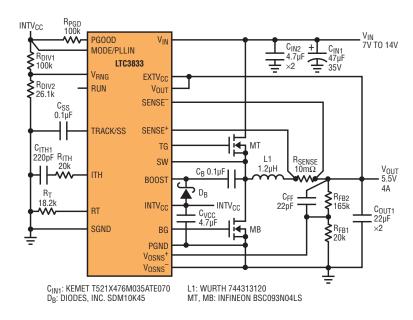

Figure 3. 14V input, 5.5V output, 4A, 2MHz step-down converter. The LTC3833 can operate at switching frequencies above the AM radio band (f > 1.8MHz) allowing the AM radio to sufficiently filter switching noise and EMI emanating from the step-down converter.

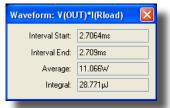

Figure 4. 24V input, 1.8V output, 15A, 2MHz step-down converter. The LTC3833 can achieve very low on-times, which allows for a single-stage converter design. Using a traditional controller with longer minimum on-times would require two or more stages, which would mean a costlier, bigger and less efficient design.

board traces can cost several percentage points in regulation accuracy.

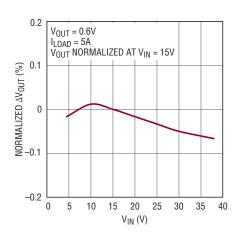

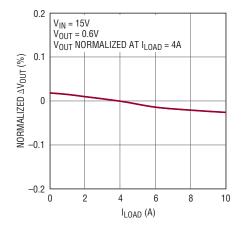

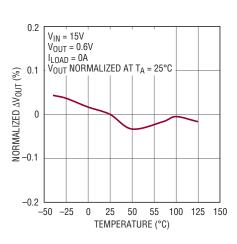

Remote differential output sensing and an accurate internal reference combine to give the LTC3833 excellent output regulation accuracy over line, load and temperature, even when there are offsets caused by trace losses on the PC board. The LTC3833 is able to achieve output accuracy figures of  $\pm 0.25\%$  at  $25^{\circ}$ C,  $\pm 0.67\%$  from  $0^{\circ}$ C to  $85^{\circ}$ C and  $\pm 1\%$ from  $-40^{\circ}$ C to  $125^{\circ}$ C. Total accuracy that accounts for line, load and remote ground variations are  $\pm 1\%$  from  $\circ^{\circ}$ C to 85°C and  $\pm 1.5\%$  from  $-40^{\circ}$ C to 125°C. Figure 5 illustrates typical regulation accuracy that could be expected from the LTC3833 over line, load and temperature.

Conventional schemes for remote differential output sensing involves a unity gain differential amplifier that senses the remote output and remote ground terminals directly (Figure 6). The output of this amplifier is then scaled down through an external resistor divider (which also programs the output voltage) and fed back into the core controller. In addition to greater design effort involved with this scheme, input and/ or output common mode range limitations of the unity gain amplifier can reduce the range of output voltages where remote differential sensing can be used.

Remote differential output sensing is seamless in the LTC3833. It is simple to use, requires minimal, if any, design effort, and requires less area than other remote sensing schemes. As in traditional feedback sensing, the output is sensed through a

#### Figure 5. Typical regulation accuracy of the LTC3833 over line, load and temperature

The LTC3833 features true remote differential output sensing. This allows for accurate regulation of the output even in high power distributed systems with heavy load currents and shared ground planes. Remote differential sensing is critical for low output voltages, where small offsets caused by parasitic IR drops in board traces can cost several percentage points in regulation accuracy.

resistor divider network that is used to program the output voltage. The LTC3833 takes this one step further by sensing the output's remote ground terminal where the other end of the resistor divider network is terminated. Therefore, output voltage programming is similar to other feedbacksensing controllers, but with the advantage that the LTC3833 is able to correct for board losses and offsets. The LTC3833 is invaluable when regulation accuracy

is required in high power, high current distributed applications where multiple systems share power and ground planes.

The LTC3833 is designed to handle remote ground offsets as large as ±500mV with respect to local ground. This includes the ability to soft-start smoothly from an initial condition state where the output of the regulator is sitting 500mV below local ground.

#### **OTHER FEATURES**

**Programmable Current Limit** As a valley current mode controller, the LTC3833 senses and controls the valley point of the inductor current in order to maintain output regulation. The inductor current is sensed with a sense resistor in series with the inductor or by sensing the inductor's DCR voltage drop through a RC network across the inductor. Either way, the inductor current is continuously sensed in all switching cycles, which allows accurate and fast control of the output current including output current limit.

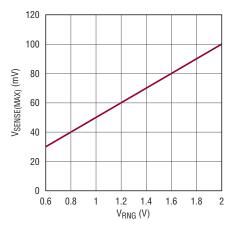

The LTC3833 allows programming the output current limit through the voltage on VRNG pin, providing an extra degree of freedom when choosing inductors and sense resistors for a given application. The maximum current sense voltage across the sense resistor or inductor's DCR can be programmed continually from 30mV to 100mV. Figure 7 shows the maximum current sense voltage as a function of the VRNG voltage.

#### EXTV<sub>cc</sub> and INTV<sub>cc</sub>

The LTC3833 has an internal 5.3V low dropout regulator that powers internal control circuitry including the strong high and low side gate drivers, and is available to the outside world through the INTV<sub>CC</sub> pin. The INTV<sub>CC</sub> regulator can source a maximum of 50mA while maintaining good regulation, so it can be used in moderation as a supply to power external circuitry or as a bias voltage source. An external supply source ( $\geq$ 4.8v) can be connected to EXTV<sub>CC</sub> pin to bypass the internal regulator. This is especially The LTC3833 also features a continuously programmable current limit,  $EXTV_{CC}$ , selectable pulse-skipping or forced continuous modes, run enable, supply tracking and soft-start.

useful for high  $v_{IN}$  applications where the internal linear regulator becomes less efficient. If the LTC3833 switching regulator is generating a 5V output, it can be connected back to EXTV<sub>CC</sub> (shown in Figures 3 and 8). This scheme can increase overall efficiency by 2%–3% versus using the internal 5.3V regulator.

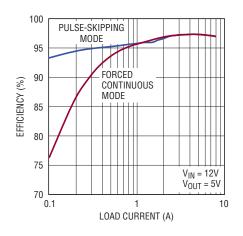

Pulse-Skipping or Forced Continuous Mode at Light Loads

The LTC3833 offers two modes of operation at light loads to best meet the requirements of a given application. For applications that require high efficiency at light loads, the LTC3833 can be programmed for pulse-skipping mode (by tying MODE/PLLIN pin to GND), which allows the switching regulator to transition into discontinuous conduction mode, thus increasing efficiency by lowering the number of switching

VII

INTV<sub>CC</sub>

RNG

Figure 7. The LTC3833 provides a programmable current limit.

cycles. The downsides of pulse-skipping mode are the variable switching frequency (dependent on load current) and a slightly higher output voltage ripple.

On the other hand, for applications that require predictable EMI performance and

V<sub>IN</sub> 7V TO 38V value constant switching frequency or require very accurate regulation at light loads, the LTC3833 can be programmed for forced continuous mode (by tying MODE/PLLIN pin to INTV<sub>CC</sub>). In forced continuous mode, the LTC3833 maintains the programmed switching frequency even at no load, but sacrifices light load efficiency in the process. Figure 8 shows an example of the differences in efficiency between the two modes.

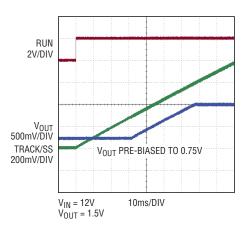

#### Soft-Start and Tracking

The LTC3833 provides soft-start—either from zero or prebiased output voltage condition (Figure 9)—and external tracking capability through the TRACK/SS pin. The soft-start time and ramp rate can be programmed by a capacitor from TRACK/SS pin to GND. This capacitance and the 1µA current source out of the TRACK/SS pin determine the soft-start time

Figure 8. 38V input, 5V output, 8A, 200kHz step-down converter. The LTC3833 offers two modes of operation at light loads: pulse-skipping mode for higher efficiency or forced continuous mode for constant switching frequency.

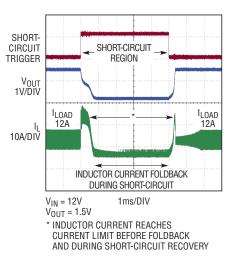

The LTC3833 acts quickly and effectively to protect the output and external components of the switching regulator if the output encounters overvoltage, overcurrent and short-circuit conditions.

and ramp rate. The output reaches its final programmed value when TRACK/SS voltage reaches 0.6v, the internal reference voltage for the LTC3833. Alternatively, an external ramp can drive the TRACK/SS pin in order to track the output of the switching regulator to the external ramp, providing better control of power-up and power-down conditions of the switching regulator.

#### **Run Enable**

The LTC3833 provides a dedicated enable/ disable function through the RUN pin. The LTC3833 self-enables when the RUN pin is left floating. It is disabled or shut down by forcing RUN to GND. The quiescent current of the LTC3833 in shutdown is 15µA. The LTC3833 is enabled when RUN is pulled greater than 1.2V, which is an accurate, well-controlled threshold. This allows the RUN pin to be programmed as an input undervoltage lockout if desired by programming a resistor divider from  $v_{IN}$  to RUN to GND. The RUN pin can also sink about 35µA of current, allowing it to be pulled directly up to  $V_{IN}$  through a sufficiently large pull-up resistor.

**Power Good and Fault Protection** The LTC3833 acts quickly and effectively to protect the output and external components of the switching regulator if the output encounters overvoltage, overcurrent and short-circuit conditions. The programmed current limit prevents overcurrent conditions and allows the output to droop down when the output current exceeds current limit. During short-circuit conditions, the LTC3833 forces foldback current limiting, where the current limit is progressively lowered to about a quarter of the programmed current limit for a hard short at the output (Figure 10).

Overvoltage conditions are handled by forcing the low side power MOSFET to turn on to discharge the overvoltage at the output.

The LTC3833 provides a power good function through the PGOOD pin, which is an open drain output that is resistively pulled up to a logic level voltage (or  $INTV_{CC}$ ) externally. If the output is within  $\pm 7.5\%$  of the programmed value, then PGOOD is high, indicating power is good.

#### CONCLUSION

The LTC3833 is a synchronous stepdown DC/DC controller that can meet the demands of high current, low voltage applications while remaining versatile enough to fit a wide range of step-down DC/DC applications.

It provides the usual set of features such as soft-start, power good and fault protection commonly available with step-down controllers. It also adds some invaluable extras, including remote output sensing, programmable current limit, external clock synchronization and EXTV<sub>CC</sub>. It also features high performance specs, including 0.67% output accuracy, switching frequency (up to 2MHz) above the AM radio band, high step-down ratios through a 2ons minimum on-time, and quick response time to transient conditions in the line and load. ■

Figure 9. The LTC3833 can smoothly start up into a prebiased output.

Figure 10. During a short circuit at the output, the LTC3833 reduces the output current to 1/4 of programmed current limit.

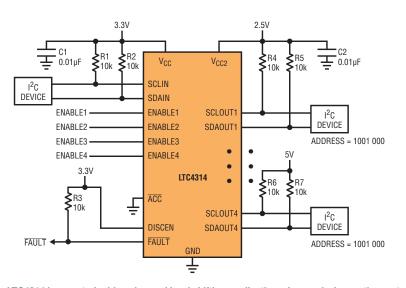

## 2-Channel and 4-Channel Pin-Selectable I<sup>2</sup>C Multiplexer Features High Noise Margin, Capacitance Buffering, Level Translation and Stuck Bus Recovery

**Rajesh Venugopal**

The inherent simplicity of I<sup>2</sup>C and SMBus 2-wire protocols has made them a popular choice for communicating vital information in large systems. Both standards employ simple open-drain pull-down drivers with resistive or current source pull-ups. Nevertheless, several practical problems arise as systems grow in complexity.

The first problem with large systems is that devices with hard-wired I<sup>2</sup>C addresses require address expansion to prevent conflicts. Second, noise causes glitches that can be interpreted as legitimate clock or data transitions, compromising data reliability. Third, I<sup>2</sup>C devices can cause the bus to stick low. Finally, timing specifications are increasingly difficult to meet, and clock frequencies are limited by the equivalent bus capacitance, which increases with system size and complexity. The LTC4312 and LTC4314 pin-selectable 2-channel and 4-channel I<sup>2</sup>C multiplexers with bus buffers address these issues with a number of powerful features (see Table 1). Since these two devices share the same features, except for the number of channels, this article focuses on the LTC4314.

An upstream I<sup>2</sup>C bus (SDAIN, SCLIN) can be connected to any combination of downstream buses through the LTC4314's bus buffers and multiplexer switches by driving the ENABLE pins of the desired output buses high. Multiple devices having the same address can be placed on different buses and isolated using the ENABLE pins, thereby achieving address expansion. The buffers provide capacitance isolation between the upstream bus and the downstream buses, allowing for partitioning of the bus capacitance. In single supply systems, the buffers regulate the bus up to  $0.33 \cdot v_{CC}$ , providing a large logic low noise margin. Rise time accelerators (RTAs) of appropriate strength can be activated to overcome bus capacitance limitations, reduce rise time and allow for higher switching frequencies even when operating with heavy loads.

The LTC4314 is compatible with the I<sup>2</sup>C standard and Fast Mode, SMBus and PMBus specifications. Stuck bus recovery circuitry disconnects the upstream bus from downstream buses when SDA and SCL have not been simultaneously high at least once in 45ms, freeing the upstream bus to resume communications. The recovery circuitry also attempts to convince

| FEATURE                                     | BENEFITS                                                                                                                                                                                      |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2- and 4-Pin Selectable<br>Downstream Buses | <ul> <li>Maximum flexibility of bus configurations</li> <li>Address expansion when used as a MUX</li> </ul>                                                                                   |

| I <sup>2</sup> C Buffers                    | • Breaks up bus capacitance, which allows large $I^2C$ compliant systems to be built, by keeping the capacitance of each section < 400pF                                                      |

| Selectable $V_{IL}$                         | <ul> <li>High logic low noise margin up to 0.33 • V<sub>CC</sub></li> <li>Selectable RTA Operating voltage range</li> </ul>                                                                   |

| Level Translation                           | • Provides I <sup>2</sup> C communication between 1.5V, 1.8V, 2.5V, 3.3V and 5V buses                                                                                                         |

| Rise Time Accelerators<br>(RTAs)            | <ul> <li>Reduce rise time</li> <li>Allow larger bus pull-up resistors for better noise margin</li> <li>Selectable RTA pull-up current strength</li> </ul>                                     |

| Disconnection and Recovery from Stuck Bus   | <ul> <li>Free masters to resume upstream communications</li> <li>Generates up to to 16 clock pulses and a stop bit on the stuck buses to convince the stuck device to release high</li> </ul> |

#### Table 1. Key features of the LTC4312 and LTC4314

The LTC4314 is compatible with the I<sup>2</sup>C standard and Fast Mode, SMBus and PMBus specifications. Stuck bus recovery circuitry disconnects the upstream bus from downstream buses when SDA and SCL have not been simultaneously high at least once in 45ms, freeing the upstream bus to resume communications.

the stuck device to release high by generating up to 16 clock pulses and a stop bit on the enabled downstream buses.

Finally, cards can be hot-swapped into and out of the LTC4314's  $1^2$ C output buses provided that the channel being hotswapped has been disabled. The LTC4314's operating voltage range is  $v_{CC}$  from 2.9V to 5.5V,  $v_{CC2}$  from 2.25V to 5.5V and bus voltages from 2.25V to 5.5V. The LTC4314 can level translate down to 1.5V and 1.8V buses under certain conditions if RTAs are disabled on the low voltage bus.

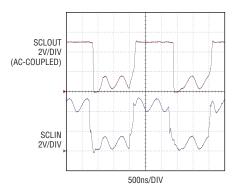

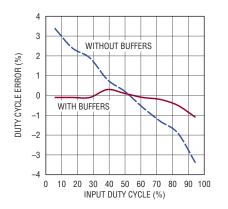

#### HIGH BANDWIDTH BUFFERS IMPROVE NOISE MARGIN AND SPEED WHILE MAINTAINING LOW OFFSET High noise margin is obtained by leaving the LTC4314 buffers on until both the input and output bus voltages are > $0.33 \cdot V_{MIN}$ , where $V_{MIN}$ is the lower of the $V_{CC}$ and

where  $v_{MIN}$  is the lower of the  $v_{CC}$  and  $v_{CC2}$  voltages. This is possible because

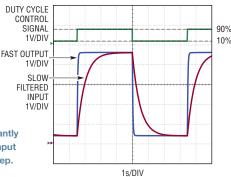

Figure 1. The LTC4314 transmitting a noisy 400kHz I<sup>2</sup>C signal applied to SCLIN. The SCLOUT1 waveform tracks SCLIN when SCLIN is a logic low. During logic highs, noise on SCLIN above 0.33 •  $V_{MIN}$  is not propagated to SCLOUT.

the high bandwidth buffers do not limit the rise rate of the bus, permitting them to stay on to a higher bus voltage.

As seen in Figure 1, when a noisy 400kHz square wave signal is applied to SCLIN, the SCLOUT1 waveform tracks SCLIN when

the SCLIN voltage is < 0.33 • V<sub>MIN</sub>, and releases high when the SCLIN voltage is > 0.33 • V<sub>MIN</sub>. The low offset makes the SCLOUT1 waveform almost identical to the SCLIN waveform for voltages < 0.33 • V<sub>MIN</sub>. No output glitches occur as the input crosses the V<sub>IL</sub> level of 0.33 • V<sub>MIN</sub>, as seen in the SCLOUT1 waveform.

As the buffers are disconnected when both input and output bus voltage are >  $0.33 \cdot V_{MIN}$ , any noise applied to the logic high state on one side is not propagated to the other side as long as that bus voltage does not drop below  $0.33 \cdot V_{MIN}$ . This is seen in Figure 1 where the logic high state of SCLOUT1 is unaffected by noise on SCLIN.

Designers who are in control of the entire I<sup>2</sup>C system can set the LTC4314 to operate at frequencies of up to 1MHz by adjusting the RC load on the bus and using strong RTAS (see Table 2). The LTC4314's highto-low propagation delay t<sub>PDHL</sub> is always positive, on the order of 100ns. Depending on bus loading conditions on the upstream and downstream sides of the LTC4314, the low-to-high propagation delay t<sub>PDLH</sub> of the LTC4314 can be either positive or negative. For systems operating at high frequencies (>400kHz) designers should quantify the t<sub>PDLH</sub>-t<sub>PDHL</sub> skew in their SDA and SCL pathways and ensure data set-up and hold times are acceptable on all buses.

Figure 2. The LTC4314 in a nested addressing and level shifting application where a device on the upstream 3.3V bus communicates with devices on the 2.5V and 5V downstream buses. Only buses 1 and 4 are shown for simplicity.

12 | October 2011 : LT Journal of Analog Innovation

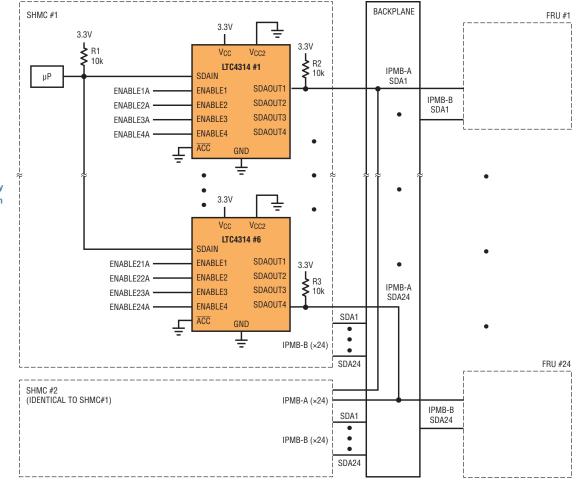

Figure 3. The LTC4314 used in a radially connected telecommunications system in a 6 × 4 arrangement. The ENABLE pins of only one shelf manager are high at any given time. Only the SDA pathway is shown for simplicity.

### LEVEL TRANSLATION AND NESTED ADDRESSING

The circuit shown in Figure 2 illustrates level translation and nested addressing features of the LTC4314. The LTC4314 can level translate the input and output buses to voltages between 2.25V (1.5V and 1.8V under some circumstances) and 5.5V. In Figure 2 the LTC4314 translates a 3.3V input to 5V and 2.5V outputs. Only downstream buses 1 and 4 are shown for simplicity. Each output channel has a dedicated ENABLE pin select that allows the master to communicate independently with slave devices with identical 1<sup>2</sup>C addresses provided that only one downstream bus is enabled at a time.

#### RADIALLY CONNECTED TELECOMMUNICATIONS APPLICATION

Figure 3 shows the LTC4314 used in a radially connected telecommunications application such as ATCA. Two shelf managers (SHMCs) are used to communicate with slave 12C devices for redundancy. Each shelf manager can have as many LTC4314s as required depending on the number of boards in the system and the desired radial/star configuration (6  $\times$  4 in Figure 3). The ENABLE pins inside only one shelf manager are asserted high at any time. Since the LTC4314 can be cascaded with other Linear Technology bus buffers, up to 24 FRUs with Linear Technology bus buffers on their edges can be plugged into the backplane.

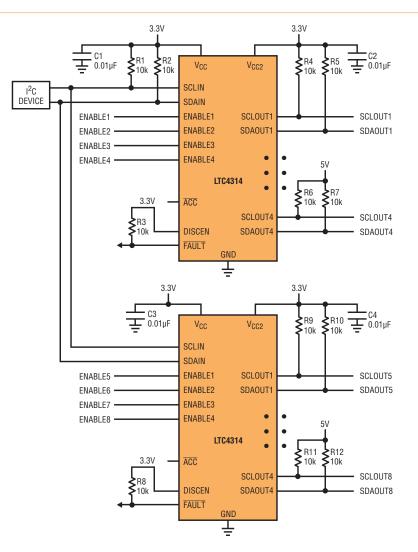

#### **PARALLELING LTC4314s TO ACHIEVE MULTIPLEXING OF MORE BUSES** Multiple LTC4314s can be connected in parallel to perform higher order multiplexing. Figure 4 shows a 1:8 multiplexer using two LTC4314s.

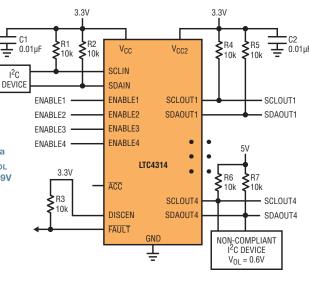

#### INTEROPERABILITY WITH NONCOMPLIANT I<sup>2</sup>C DEVICES

The high buffer turn-off voltage of the LTC4314 ensures interoperability with noncompliant I<sup>2</sup>C devices that drive a high  $v_{OL} > 0.4v$ . This is shown in Figure 5 where a noncompliant device on channel 4 drives a high  $v_{OL} = 0.6v$ . The buffer turn-off voltage is 1.089v, yielding a logic low noise margin of > 0.4v at both the input and output.

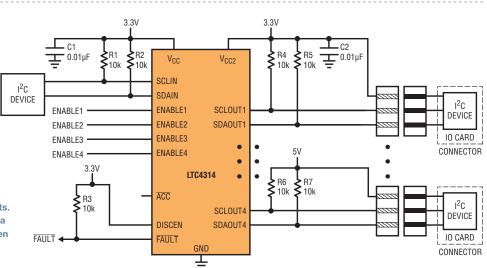

#### **HOT SWAP™ APPLICATION**

I/O cards can be hot swapped into the downstream buses of an LTC4314 residing on a live backplane as shown in Figure 6. Before plugging or unplugging an I/O card, care must be taken to disable the corresponding output channel so that the card does not disturb any I<sup>2</sup>C transaction that may be in progress. The connection to the inserted card must be enabled only when all ongoing transactions on the bus have completed and the bus is idle.

### STUCK BUS DETECTION AND RECOVERY

Occasionally, slave devices get confused and get stuck in a low state. The LTC4314 monitors the enabled output buses to detect if clock and data have been simultaneously high at least once in 45ms. If this condition is not detected, the LTC4314 asserts the FAULT flag low. If DISCEN is tied high, the LTC4314 also disconnects the input and output sides and generates clock pulses on the enabled downstream buses in an attempt to free the stuck bus. Clocking is stopped when data releases high or 16 clocks have been

Figure 5. The LTC4314 in operation with a noncompliant  $I^2C$  device that drives a V<sub>OL</sub> = 0.6V. The buffer turn-off voltage is 1.089V yielding a logic low noise margin > 0.4V.

Figure 4. Paralleling LTC4314 devices to realize a 1:8 multiplexer

generated, whichever comes first. After the final clock pulse, a stop bit is generated to reset the bus for further communication.

A rising edge on one or more ENABLE pins, after all ENABLES have been taken low, is required to reestablish connection between the input and output. Doing this also clears the FAULT flag. The master can wait for the fault condition to clear (FAULT released high), either on its own or through the 16 clock pulses issued by the LTC4314, before toggling the LTC4314'S ENABLE pins, or it can do so preemptively before the fault has cleared to reestablish connection. The master can then take appropriate action to clear the stuck low condition.

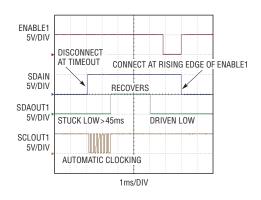

Figure 7 shows the waveforms during an SDAOUT1 stuck low and recovery event. After the 45ms timeout period has elapsed, the FAULT flag is asserted low and the input and output sides are disconnected. This causes SDAIN to release high.

14 | October 2011 : LT Journal of Analog Innovation

#### design features

|                                                                                                         | ACC  | I <sub>RTA</sub> | V <sub>RTA(TH)</sub>   | VIL,RISING              |

|---------------------------------------------------------------------------------------------------------|------|------------------|------------------------|-------------------------|

|                                                                                                         | Low  | Strong           | 0.8V                   | 0.6V                    |

| Table 2. ACC control of the rise time accelerator current                                               | Hi-Z | 3mA              | 0.4 • V <sub>MIN</sub> | 0.33 • V <sub>MIN</sub> |

| $I_{\mbox{\scriptsize RTA}}$ and buffer turn-off voltage $V_{\mbox{\scriptsize IL,RISING}}(\mbox{typ})$ | High | None             | N/A                    | 0.33 • V <sub>MIN</sub> |

Figure 6. The LTC4314 in a Hot Swap<sup>™</sup> application where cards are being plugged in to or unplugged from the outputs. The corresponding ENABLE pin must be driven low before a card can be plugged or unplugged and should only be driven high when the other buses are idle.

Clock pulses are generated on SCLOUT1. SDAOUT1 releases high before 16 clock pulses have been generated. Clock pulsing is stopped and a stop bit is generated. When the ENABLE1 pin is toggled, a connection is established between the input and output and a driven low level on SDAOUT1 is propagated to SDAIN.

If automatic stuck bus disconnection is not desired, this feature can be disabled by tying DISCEN low. In this case, during a stuck bus event, the FAULT flag is asserted low, but no stop bit or clock generation occurs and the input and output sides stay connected.

#### **RISE TIME ACCELERATORS**

The rise time accelerators (RTAs) of the LTC4314 can be configured either in current source mode ( $\overline{ACC}$  open), slew limited switch mode ( $\overline{ACC}$  grounded), or disabled ( $\overline{ACC}$  high). In the current source mode the RTAs source a constant 3mA current into the bus. In the slew controlled switch mode, the RTAs turn on in a controlled manner and source current

into the buses making them rise at a typical rate of  $40V/\mu s$ . The RTA current and the buffer turn-off voltage are selected by the  $\overline{ACC}$  setting as shown in Table 2.

For heavily capacitive buses with low to moderate noise, tie  $\overline{ACC}$  low to meet system rise times and maximize SCL switching frequency. Tying  $\overline{ACC}$  low provides the strongest pull-up current over the maximum voltage range. For higher noise immunity, leave  $\overline{ACC}$  open or tie it to 0.5 • V<sub>CC</sub> to set the buffer V<sub>IL</sub> to

Figure 7. Bus waveforms during a SDAOUT1 stuck low and recovery event 0.33 •  $V_{MIN}$  and to get 3mA of RTA current. The 3mA RTA current is enough to meet the 1µs standard mode I<sup>2</sup>C rise time requirement (100kHz operation) for bus capacitances up to 690pF with DC bus pull-up currents < 4mA. Tie ACC high if no acceleration is needed. To selectively disable RTAs only on the outputs, ground  $V_{CC2}$ and either ground ACC or leave ACC open.

#### CONCLUSION

The LTC4314 and LTC4312 are pin-selectable I<sup>2</sup>C multiplexers that solve practical design issues associated with large I<sup>2</sup>C bus systems by providing capacitance buffering, nested addressing and level translation. These parts maintain a low offset and high logic low noise margin up to 0.33 ● V<sub>CC</sub>. Their high bandwidth buffers and integrated RTAs allow for operation at frequencies up to 1MHz with guaranteed stability from zero to 1.2nF capacitive loads. They also disconnect and recover buses when buses are stuck low and allow I/O cards to be hot swapped into and out of live systems.

# Low $I_Q$ , High Efficiency Dual Output Controllers for Wide Ranging Input and Output Voltages

Jason Leonard

The LTC3857 and LTC3858 are versatile low quiescent current ( $I_{Q}$ ), 2-phase dual output synchronous buck controllers that are ideal for applications demanding high efficiency and minimal power loss over a broad range of load currents, from virtually no load to many amps. They feature a wide input supply range of 4V to 38V (40V abs max) that covers a broad range of battery chemistries and power sources. Each output can be set from 0.8V to 24V (28V abs max).

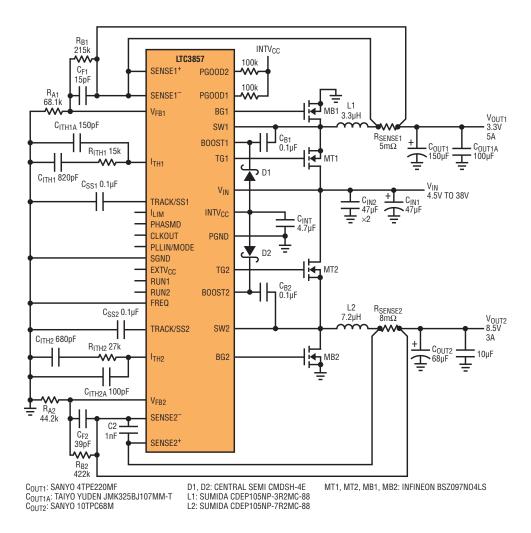

The LTC3857 and LTC3858 are pin-compatible parts that differ only slightly, most notably in short-circuit operation and at light load operation. These differences are discussed below and summarized in Table 1. A "-1" version of each is available with slightly fewer features (Table 2). The LTC3857/LTC3858 are also mostly pin compatible with the popular LTC3827/LTC3826 family of low I<sub>Q</sub> controllers. Figure 1 shows a typical application circuit in which the LTC3857 is used to convert a widely varying car battery voltage to two well regulated outputs.

#### LOW I<sub>Q</sub> EXTENDS BATTERY RUN TIME

In many applications, one or more supplies remain active at all times, often in a standby mode where little or no load current is drawn. In these "always-on" systems, the quiescent current of the power supply circuit represents the vast majority of the current drawn from the input supply (battery). Having a low IO power supply is crucial to extending battery run times. In Burst Mode® operation, the LTC3857 draws only 50µA when one output is active and only 65µA when both outputs are enabled, while the LTC3858 draws 170µA when one output is active and only 300µA when both outputs are enabled. Both devices consume only 8µA when both outputs are shut down.

Figure 1. High efficiency dual output 3.3V/8.5V step-down converter. The 8.5V output follows V when V is less than 8.5V.

16 | October 2011 : LT Journal of Analog Innovation

In "always-on" systems, the quiescent current of the power supply circuit represents the vast majority of the current drawn from the input supply (battery). Having a low  $I_Q$  power supply is crucial to extending battery run times.

#### Table 1. Key differences between the LTC3857 and LTC3858

| FEATURE                                    | LTC3857                                               | LTC3858                                                                                         |

|--------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Quiescent Current<br>(One Channel On)      | 50µA                                                  | 170μΑ                                                                                           |

| Quiescent Current<br>(Both Channels On)    | 65µA                                                  | 300µA                                                                                           |

| Burst Mode Operation                       | Lowest Ripple                                         | Highest Midrange Efficiency                                                                     |

| Short-Circuit Protection                   | Cycle-by-Cycle Current Limiting with Current Foldback | Cycle-by-Cycle Current Limiting with<br>Current Foldback and<br>Optional Short-Circuit Latchoff |

| Output Voltage Tracking<br>During Start-Up | Yes, Tracking or Soft-Start<br>(TRACK/SS Pin)         | No, Soft-Start Only (SS Pin also Used for Short-Circuit Latchoff Timer)                         |

#### **OPERATING MODES**

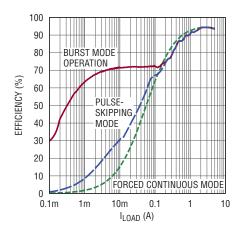

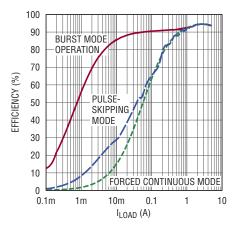

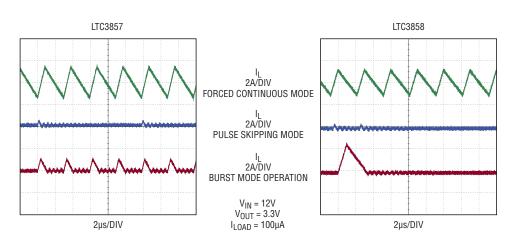

The PLLIN/MODE pin is used to program one of three modes at low load currents— Burst Mode operation, pulse-skipping mode, or forced continuous mode. Forced continuous mode maintains constant frequency operation from no load to full load, at the expense of light load efficiency. Burst Mode operation is the most efficient mode at light loads, albeit with slightly higher ripple and features the lowest quiescent current. Pulse-skipping mode is somewhat of a compromise, maintaining very low ripple and moderate efficiency at light loads. Figures 2 and 3 show the efficiencies in these three modes.

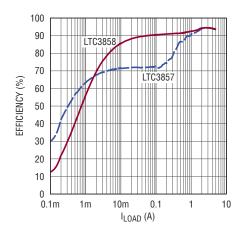

The LTC3857 and LTC3858 operate similarly to each other in forced continuous and pulse-skipping mode. There are differences in Burst Mode operation, however. The LTC3857 is optimized for the lowest quiescent current and for relatively low ripple. The LTC3858 is optimized for the highest efficiency over a broad range of load current. This means the LTC3857 transitions to constant frequency operation (with lower ripple) at a lower load current than the LTC3858, while the LTC3858 maintains higher efficiency (with higher ripple) at intermediate light loads (Figures 4 and 5).

Figure 2. Efficiency of in the circuit of Figure 1 using the LTC3857. Efficiencies are shown for the three modes of operation (forced continuous, pulseskipping, and Burst Mode operation). At heavier loads, the efficiency is independent of the mode.

#### CURRENT SENSING, CURRENT LIMIT AND SHORT-CIRCUIT PROTECTION

The LTC3857/LTC3858 each uses a peak current mode architecture. A high speed rail-to-rail differential current sense comparator constantly monitors the voltage across a current sense element, either a sense resistor or the inductor's DC resistance (as derived from an R-C network). The peak sense voltage is set by the threestate ILIM pin (fixed on the "-1" version). If a short circuit occurs, current limit foldback reduces the peak current to minimize the dissipation in the power components. Foldback is disabled during start-up for predictable tracking or soft-start.

The LTC3858 has an additional feature that further protects during a short-circuit event. The ss pin can be used as a shortcircuit timer. If the short circuit lasts long enough, the output "latches off" and stops

Figure 3. Efficiency of in the circuit of Figure 1 using the LTC3858. Note that the efficiencies in forced continuous and pulse-skipping modes are essentially identical to the LTC3857's in Figure 2 only Burst Mode operation is different at light to intermediate loads.

switching. The latch can only be reset by cycling the RUN pin or by cycling the input power ( $v_{IN}$ ). This latchoff feature can be defeated by connecting a resistor between the ss and INTV<sub>CC</sub> pins. The two channels of the LTC3858 operate independently; i.e., a short-circuit latchoff on one channel does not affect the other channel.

Although both current foldback and latchoff provide additional levels of protection during a short-circuit event, the LTC3857/LTC3858 is fundamentally protected by its current mode architecture. The current comparator is always active, meaning switching cycles can be gracefully skipped as needed to keep the inductor current under control at all times.

#### OTHER IMPORTANT FEATURES

The FREQ pin is used to set the switching frequency. Tying this pin to ground selects 350kHz while tying it to INTV<sub>CC</sub> selects 535kHz. Connecting a single resistor from this pin to ground allows the frequency to be set anywhere from 50kHz to 900kHz. A short minimum on-time of 95ns allows low duty cycle operation even at high frequencies. The maximum 99% duty cycle capability allows low dropout operation for low input/ high output voltage applications.

An internally compensated phase-locked loop (PLL) enables the LTC3857/LTC3858 to synchronize to an external clock source (applied to the PLLIN/MODE pin) from 75kHz to 850kHz. When synchronized, the LTC3857/LTC3858 operates in forced continuous mode to maintain constant frequency operation independent of the load current. When the external clock is absent or momentarily interrupted, the LTC3857/LTC3858 operates at the frequency set by the FREQ pin. The internal PLL filter is prebiased to a voltage corresponding to this free-running frequency. When an external clock is detected, the PLL is enabled. Since the PLL filter is prebiased and barely has to

Figure 4. Inductor current ripple at 12V to 3.3V at 100µA load current. The LTC3857 and LTC3858 differ only in Burst Mode operation.

charge or discharge during this transition, synchronization is achieved quickly, with only small changes in frequency and minimal output voltage ripple.

The MOSFET drivers and control circuits are powered by  $INTV_{CC}$ , which by default is generated from an internal low dropout (LDO) regulator from the main input supply pin ( $v_{IN}$ ). The strong gate drivers with optimized dead time control provide high efficiency at heavy loads. To reduce power dissipation due to MOSFET gate charge losses and improve efficiency at high input voltages, a supply between 5v and 14v (abs max) can be connected to

Figure 5. Comparison of the LTC3857 and LTC3858 efficiency when configured for Burst Mode operation (PLLIN/MODE pin connected to ground) for the Figure 1 circuit. At very light to virtually no load, the LTC3857 has the lowest power loss due to its low  $I_Q$ . At intermediate loads, the LTC3858 is more efficient, at the expense of ripple.

the EXTV<sub>CC</sub> pin. When a supply is detected on EXTV<sub>CC</sub>, the  $v_{IN}$  LDO is disabled and another LDO between EXTV<sub>CC</sub> and INTV<sub>CC</sub> is enabled. EXTV<sub>CC</sub> is commonly connected to one of the output voltages generated by the LTC<sub>3</sub>857/LTC<sub>3</sub>858.

The LTC3857/LTC3858 features a RUN pin for each channel. RUN enables the output and the INTV<sub>CC</sub> supply. The LTC3857 has a TRACK/SS pin for each channel, which acts as a soft-start or allows the output to track an external reference (e.g., another supply). The LTC3858 has a dual-function ss pin for each channel. ss is used for soft-start (like the TRACK/SS pin on the LTC3857 but without tracking) and also as the optional short-circuit latchoff timer.

#### IDEAL FOR AUTOMOTIVE APPLICATIONS

The LTC3857, in particular, is well suited for automotive applications, including navigation, telematics and infotainment systems. The wide input voltage range is high enough to protect against double battery and load dump transients, while low enough to allow continuous operation during cold crank and engine start. The ultralow 50µA quiescent current is ideal for always-on supplies that are enabled even when the ignition is off. The wide output voltage range supports the higher voltage rails often used for audio systems, CD/DVD players, and disk

Figure 6. 2-phase single output application. Multiple LTC3857/LTC3858 controllers can be cascaded to drive a single output with up to 12 power stages operating out-of-phase for very high power applications.

drives. The 99% duty cycle capability provides a low dropout voltage for these rails when the battery voltage dips.

#### MULTIPHASE SINGLE OUTPUT APPLICATIONS

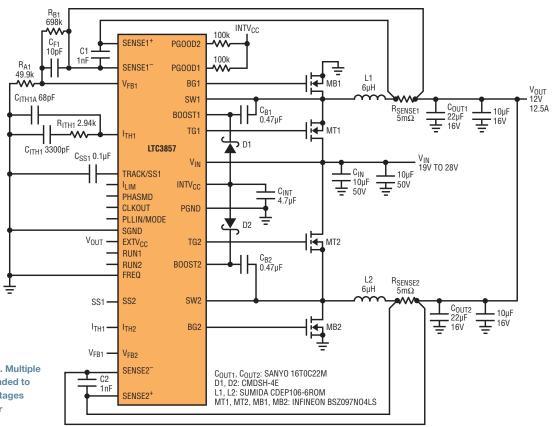

The LTC3857/LTC3858 is normally configured for two independent outputs that run 180° out-of-phase. Operating the channels out-of-phase minimizes the required input capacitance. However, the LTC3857/LTC3858 can also be configured with both power stages driving a single output. Figure 6 depicts a 19V–28V input supply generating a regulated 12V/150W output. In this configuration, both channels' compensation (ITH), feedback ( $V_{FB}$ ), enable (RUN) and soft-start (TRACK/SS or SS) pins are tied together. Since the channels operate outof-phase, the effective switching frequency is doubled, minimizing the required input and output capacitance and voltage ripple, while allowing for even faster transient response. The LTC3857/LTC3858 provides inherently fast, accurate cycle-by-cycle current sharing due to its peak current mode control architecture.

The LTC3857/LTC3858 can also be used in designs with three or more phases. The CLKOUT pin can drive the PLLIN/MODE pin of other controllers, while the PHASMD pin adjusts the relative phases of each controller. This allows 3-, 4-, 6- and 12-phase operation.

#### CONCLUSION

The LTC3857 and LTC3858 are nearly pin-compatible parts, ideal for converters requiring high efficiency over a broad load range, from no load to full load. Their low quiescent current extends operating life in battery-powered systems. They each regulate two separate outputs from 0.8v to 24v from inputs of 4v to 38v. The short minimum on-time and 99% duty cycle capability allows high frequency operation from very low to very high duty cycles. The LTC3857 and LTC3858 incorporate these features and more in 5mm × 5mm QFN and 28-lead narrow SSOP packages.

#### Table 2. Key differences between the standard and "-1" parts

|                                                | LTC3857/LTC3858                                                   | LTC3857-1/LTC3858-1                        |

|------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------|

| Current Sense Voltage                          | Adjustable 30mV/50mV/75mV<br>(ILIM pin)                           | Fixed 50mV                                 |

| Power Good Output<br>Voltage Monitor           | Independent Monitors for Each Channel<br>(PGOOD1 and PGOOD2 pins) | Monitor for Channel 1 Only<br>(PGOOD1 pin) |

| CLKOUT/PHASMD Pins for<br>Three or More Phases | Yes                                                               | No                                         |

| Package                                        | 5mm $	imes$ $5$ mm QFN                                            | 28-Lead Narrow SSOP                        |

# High Efficiency Power Supply for Intel IMVP-6/IMVP-6+/IMVP-6.5 CPUs

Jian Li and Gina Le

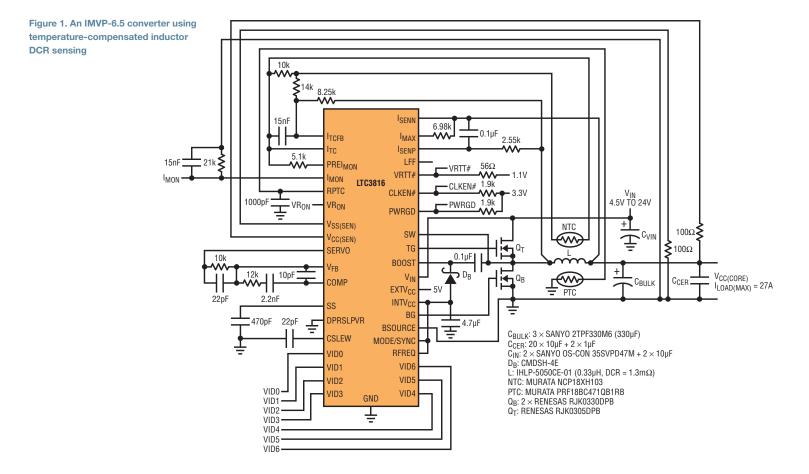

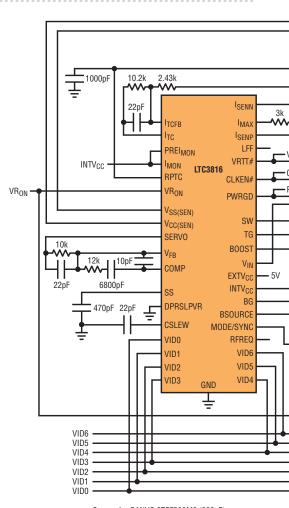

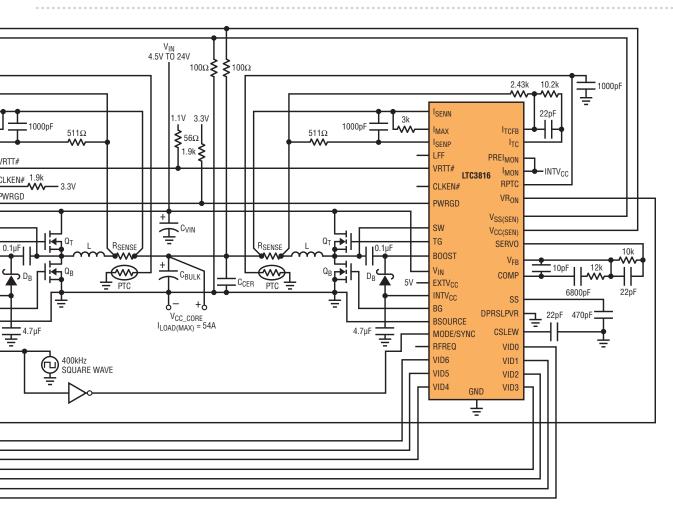

The LTC3816 is a single-phase synchronous step-down DC/DC switching regulator controller that complies with Intel Mobile Voltage Positioning (IMVP)-6/6+/6.5 specifications. It uses a constant-frequency voltage mode architecture with a leading edge modulation topology, allowing extremely low output voltages and very fast load transient response. The LTC3816 satisfies all of the IMVP-6, IMVP-6+ and IMVP-6.5 requirements, including 7-bit VID code, start-up to a preset boot voltage, differential remote output voltage sensing with programmable active voltage positioning (AVP), I<sub>MON</sub> output current reporting, power optimization during sleep state and fast or slow slew rate sleep state exit. It is suitable for a wide range of input voltages from 4.5V to 36V and output voltages up to 1.5V. The LTC3816 is available in 38-pin thermally enhanced eTSSOP and 5mm × 7mm QFN packages.

The LTC3816 meets all of Intel's IMVP-6, IMVP-6+ and IMVP-6.5 specifications in a small 5mm × 7mm 38-pin QFN. With strong gate drivers and short dead-time, the LTC3816 offers high efficiency solutions over a wide input voltage range. Its leading edge modulation topology allows very small duty cycle operation and ultrafast transient response.

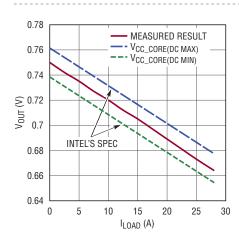

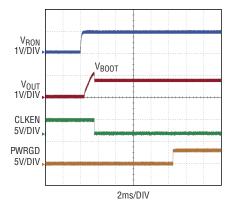

Figure 2. Load regulation with -3mV/A slope

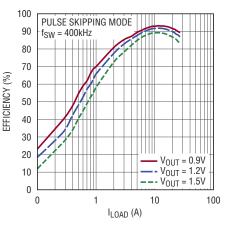

AN IMVP-6.5 CONVERTER WITH 4.5V~24V INPUT AND 27A OUTPUT Figure 1 shows an IMVP-6.5 application using temperature-compensated inductor DCR sensing. The output voltage is programmed by a 7-bit VID code. With temperature-compensated inductor DCR sensing, the LTC3816 provides an accurate –3mV/A AVP slope over temperature as shown in Figure 2. With strong integrated FET drivers and short

Figure 3. Efficiency with 12V input

dead-time, the LTC3816 offers a highly efficienct solution, as shown in Figure 3.

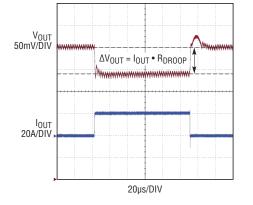

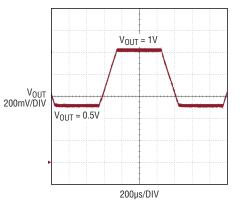

The LTC3816's leading edge modulation topology allows ultrafast transient response to meet Intel's stringent requirements. As shown in Figure 4, no undershoot other than AVP is observed during a load step-up test, easily meeting Intel's specifications. Moreover, the LTC3816 incorporates a line feedforward function to compensate for changes in the line voltage and to simplify the loop compensation. The LTC3816 feedback loop is also capable of dynamically changing the regulator output to different VID DAC voltages as shown in Figure 5. Upon receiving a new VID code, the LTC3816 regulates to its new potential with a programmable slew rate selected to prevent the converter from generating audible noise.

During start-up, the output voltage is charged to  $v_{BOOT}$  first, according to Intel's

Figure 4. Transient response with 20A load step

Figure 5. Output voltage transition from 0.5V to 1.0V in dynamic VID mode

Figure 6. Start-up test with preset boot voltage 1.1V

The LTC3816 includes an onboard current limit circuit, so that the peak inductor current can be sensed via inductor DCR or a discrete sense resistor. The LTC3816 current limit architecture allows momentary overcurrent events for a predefined duration. The LTC3816 also provides input undervoltage lockout, output overvoltage protection and PWRGD and overtemperature flags.

IMVP specification. As shown in Figure 6,  $V_{BOOT}$  is 1.1V in IMVP-6.5 and 1.2V in IMVP-6. Once the output voltage reaches  $V_{BOOT}$ , the CLKEN# output goes low and the output voltage transitions to the voltage programmed by the VID code.

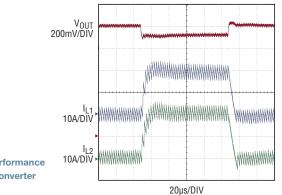

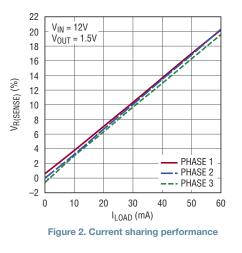

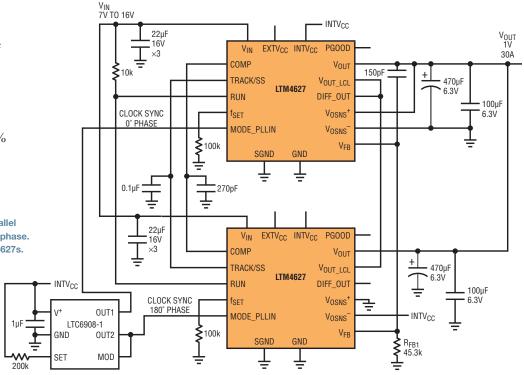

Figure 7 demonstrates that for high current applications, multiple LTC3816s can be paralleled to provide more power. The current sharing performance is very good in both static and dynamic operation conditions, as shown in Figure 8.

The LTC3816 includes an onboard current limit circuit, so that the peak inductor current can be sensed via inductor DCR or a discrete sense resistor. The LTC3816 current limit architecture allows momentary overcurrent events for a predefined duration. The LTC3816 also provides input undervoltage lockout, output overvoltage protection and PWRGD and overtemperature flags.

#### CONCLUSION

The LTC3816 meets all of Intel's IMVP-6, IMVP-6+ and IMVP-6.5 specifications in a small 5mm × 7mm 38-pin QFN. With strong gate drivers and short dead-time, the LTC3816 offers high efficiency solutions over a wide input voltage range. Its leading edge modulation topology allows very small duty cycle operation and ultrafast transient response. The LTC3816 provides high efficiency, high power density, and high reliability solutions for embedded computing, mobile computers, Internet devices and navigation displays. ■

Figure 7. A dual-channel IMVP-6 converter with 44A output using  $R_{\mbox{\scriptsize SENSE}}$  sensing configuration

$\begin{array}{l} {} C_{BULK}: 4 \times SANYO 2TPF330M6 \; (330 \mu F) \\ {} C_{CER}: 32 \times 10 \mu F + 2 \times 1 \mu F \\ {} C_{IN}: 3 \times SANYO \; OS-CON \; 35SVPD47M + 2 \times 10 \mu F \\ {} D_{B}: CMDSH-4E \\ {} L: IHLP-5050CE-01 \; (0.33 \mu H, \; DCR = 1.3m \Omega) \\ {} PTC: \; MURATA \; PRF18BC471 (DB1RB \\ {} O_{T}: \; RENESAS \; RJK0305DPB \\ {} O_{B}: 2 \times RENESAS \; RJK0330DPB \\ {} R_{SENSE}: \; PANASONIC \; ERJM1WTF1M0U \; (1m \Omega) \end{array}$

The LTC3816 feedback loop is also capable of dynamically changing the regulator output to different VID DAC voltages. Upon receiving a new VID code, the LTC3816 regulates to its new potential with a programmable slew rate selected to prevent the converter from generating audible noise.

Figure 8. Current sharing performance for a dual-channel IMVP-6 converter

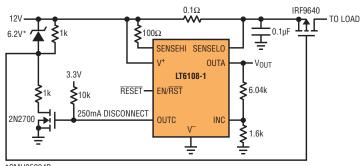

### 3A Linear Regulator Can Be Easily Paralleled to Spread Power and Heat

Todd Owen

The basic 3-terminal regulator has been a building block in designer tool kits for over thirty years without any significant change to its basic architecture. Using a fixed voltage reference, a resistor divider boosts the output voltage to the desired level. These are easy to use devices, hence their popularity, but there are some inherent downsides to this simple architecture.

One drawback to using a traditional linear regulator is that the minimum output voltage is limited to the reference voltage of the regulator. Another is that it is not easy to increase the available output current or spread power dissipation by paralleling devices. To distribute the load between multiple regulators, one must either add large ballast resistors, which incur load regulation errors, or balance

Figure 1. LT3083 block diagram

the load with complicated schemes of input sense resistors and op amp loops, which inevitably cancels out the promise of simplicity originally offered by using the ostensibly simple linear regulator.

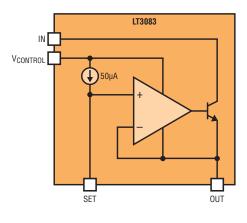

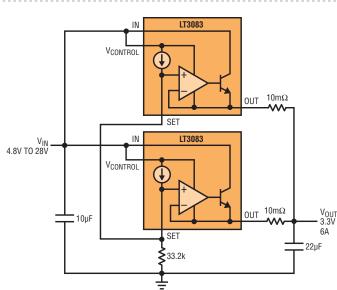

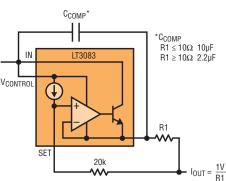

But what if the voltage reference is thrown out and replaced with a precision current source? The resulting device is deceptively simple, as shown in the block diagram of Figure 1; a precision current source connects to the noninverting input of an amplifier and the output drives a large NPN pass element and connects to the inverting input to give unity gain. This small change to the venerable linear regulator device yields enormous gains in versatility and performance.

Now, in this new architecture, connecting each of the SET pins together when paralleling regulators provides a common reference point for *all* the error amplifiers, making it possible to balance any deviceto-device offset variations with mere milliohms of ballast. Suddenly it is easy to spread power dissipation between as many devices are needed, and likewise scale the output current as necessary. The beauty of this architecture is that a single resistor generates the reference point for all of the regulators, whether one, ten or one hundred regulators are used. Additionally, the architecture allows zero resistance to equal zero output-there is no longer a fixed reference voltage to limit the bottom end of the usable output voltage range.

#### **BENEFITS OF A NEW ARCHITECTURE**

The LT<sup>®</sup>3080 1.1A linear regulator was the first linear regulator to use a precision current source architecture, making it possible to produce high current, surface mount power supplies by paralleling any number of LT3080s. The LT3083 follows in the footsteps of the LT3080 with similar high performance specifications, but with an increased 3A output current capability. The performance advantages offered by this new architecture are numerous.

#### Frequency Response and Load Regulation are Fixed

With traditional linear regulators, gain and bandwidth change as the output voltage is changed via resistor divider. Bypassing the feedback pin of the regulator affects loop response. Load regulation is not a fixed value, but a fixed percentage of the output as the resistor divider gains up any voltage deviation. Furthermore, reference voltage noise is gained up by the same resistor divider.

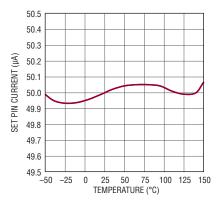

Figure 2. Reference current temperature characteristics

24 | October 2011 : LT Journal of Analog Innovation

Suddenly it is easy to spread power dissipation between as many devices are needed, and likewise scale the output current as necessary. The beauty of this architecture is that a single resistor generates the reference point for all of the regulators, whether one, ten or one hundred regulators are used.

Figure 3. Paralleling regulators for higher current and heat spreading

Using a current source and unity-gain buffer eliminates these downsides. Since the error amplifier is always in unity gain, frequency response does not change as a function of output voltage or with the use of bypassing across the reference point. Load regulation is now a fixed value, regardless of output voltage. Since bypassing does not affect loop response, two noise sources can be eliminated: the reference current noise and resistor shot noise are quieted using a single capacitor. This leaves only the error amplifier noise at the output, and again, that stays at a fixed level, no matter the output voltage.

**Top Notch DC Characteristics** DC characteristics of the LT3083 are the same as the original LT3080. The LT3083 separates out the collector of the NPN pass device to minimize power dissipation. Load regulation is typically below 1mV for the error amplifier, and nearly immeasurable on the 50µA reference current. Line regulation for the reference current is less than 0.0002%/v, and is typically  $2\mu V/v$  for the error amplifier offset. Temperature characteristics of the reference current are excellent, typically staying within 0.2% across the full operating junction temperature range, as shown in Figure 2.

The LT3083 also provides all of the protection features that Linear Technology parts are known for: current limit with safe operating area protection protects

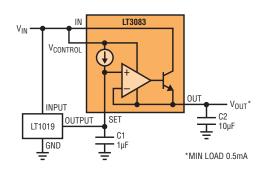

#### Figure 4. High current reference buffer

the device from damage during shortcircuit conditions and thermal limiting keeps the part safe during conditions of excessive power dissipation.

**Top Notch AC Characteristics** Don't think that the AC characteristics of the LTC3083 were sacrificed in an effort to achieve high DC performance. Transient response is excellent with as little as 10µF of output capacitance. Small ceramic capacitors can be used without the addition of ESR. Using a bypass capacitor across the reference resistor provides a slow-start function; the output voltage follows the RC time constant created by the SET resistor and bypass capacitor. Paralleling devices also provides advantages in noise performance. Paralleling multiple LT3083 regulators lowers the output noise in the same way that paralleling *n* op amps lowers noise by a factor of  $\sqrt{n}$ .

#### **APPLICATIONS**

The LT3083's deceptively simple architecture and high performance parameters make it powerful building block for applications beyond the basic linear regulator. It can be easily paralleled to increase output current and spread heat. Actively driving the SET pin is perfectly acceptable; the low offset and high output current allow for highly accurate reference supplies at high power levels. Digitally programmable supplies are achieved by driving the SET pin with a DAC. Accurate current sources are realized without tremendous difficulty. The possibilities are only limited by the creativity of the user. The LT3083 is easily configured as a 2-terminal current source, simply by adjusting the ratio of the external resistors and adding compensation.

Parallel Regulators Increase Current and Spread Heat

Figure 3 shows how to parallel multiple LT3083s to increase output current and spread heat. Note the minimal ballast needed to balance the load amongst the regulators. It's possible to produce quiet and accurate high current surface mount supplies simply by adding more LT3083s. Power dissipation is spread evenly across the paralleled regulators, but thermal management is still necessary. With as little as 0.5v drop across the regulator, a 3A load translates to 1.5w of power dissipation, pushing the thermal capabilities for surface mount designs.

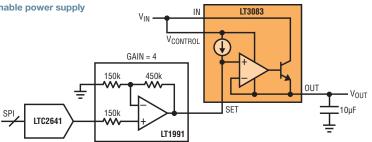

**High Current Reference Buffer** Creating a high current reference buffer takes very little effort, as shown in Figure 4. In this circuit, an LT1019-5 output connects to sink the 50µA reference current of the regulator. This reference provides 0.2% accuracy across temperature, or 10mV. With a maximum offset voltage of 4mV in the LT3083, output accuracy stays within 0.3%. The accuracy of the reference current in the LT3083 is not a factor in the output tolerance, and there are no resistors to present potential tolerance variations. **Digitally Programmed Output** Programming the output voltage digitally simply takes the addition of a DAC to drive the SET pin. Figure 4 highlights how a DAC programs the LT3083 output to anywhere from zero to over 16V within 1.5LSB. In this circuit, an LTC2641-12 using a 4.096V reference drives the SET pin of the LT3083 through the LT1991 (configured for a gain of four).

Again, the tight specifications of the LT3083 allow for such excellent performance. Keep in mind that the minimum load current requirement must be met when operating at minimum output voltages—less than 500µA loading is required when operating at low input voltages, much less than traditional linear regulators that require 5 to 10mA.

Figure 6. 2-terminal current source

**Easy 2-Terminal Current Source** Current sources can be very difficult to implement in certain applications. Some must be ground referenced, others must be referenced to a positive rail, while the most difficult designs require floating, 2-terminal devices. The LT3083 is easily configured as a 2-terminal current source, simply by adjusting the ratio of the external resistors and adding compensation as shown in Figure 5. The current source can be ground referenced, referenced to a positive rail or fully floating without concern.

#### CONCLUSION

Hiding behind the simple architecture shown in the block diagram of the LT3083 is a high performance, highly versatile, groundbreaking building block device. The LT3083 combines the architectural leap forward of the LT3080, excellent AC and DC characteristics and increased current to easily solve problems that a traditional 3-terminal or low dropout regulator cannot touch. It can be used for supplies that operate all the way down to zero volts, paralleled for high current and heat spreading, or driven dynamically. High current linear power supplies are now available for surface mount boards without sacrificing performance.

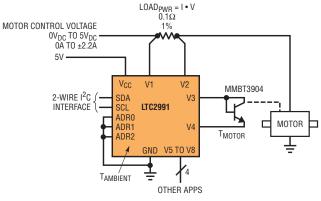

## 8-Output Regulator Powers Applications Processors

Kevin Ohlson

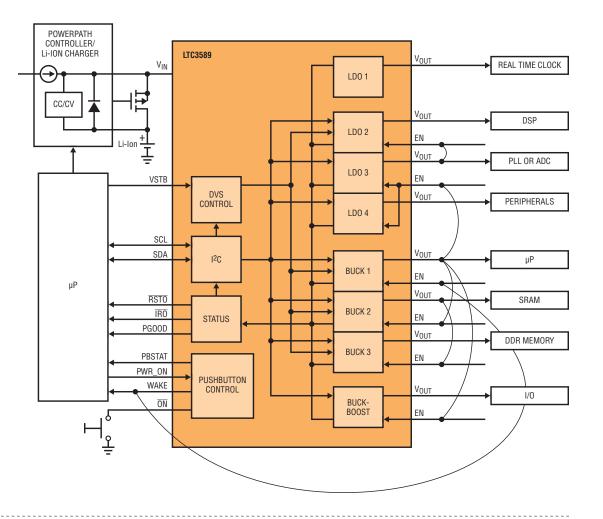

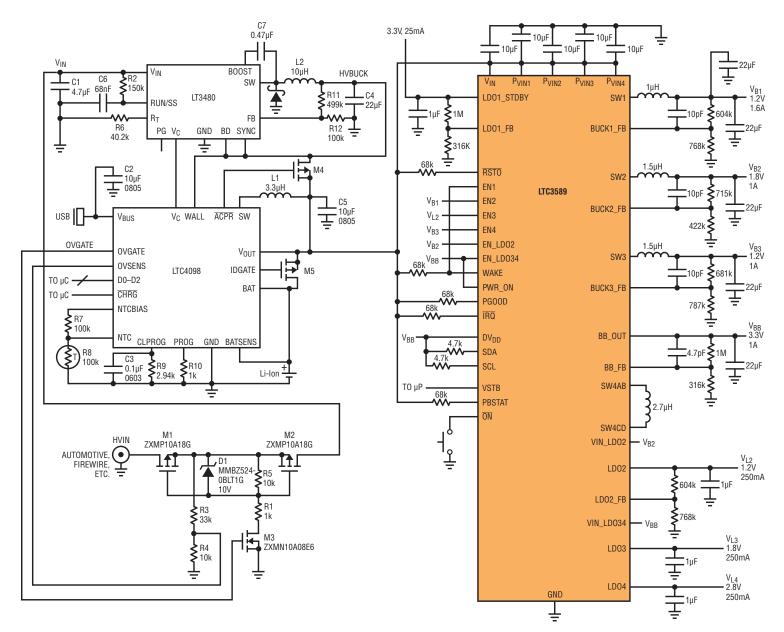

The market for applications processors, the integrated core/ memory/video/UI function chips used in smartphones, tablets, netbooks and automobile infotainment systems, is one of the fastest growing segments in electronics today. A single applications processor IC, such as one from Freescale, Marvell or an in-house custom processor, is packed with functions and requires independent power supplies for its core, I/O, memory and peripherals. The challenge is producing all those rails in limited space, at high efficiency, from a wide range of power inputs—a tablet, for instance, requires power conversion from USB, automotive battery and its built-in Li-ion battery.

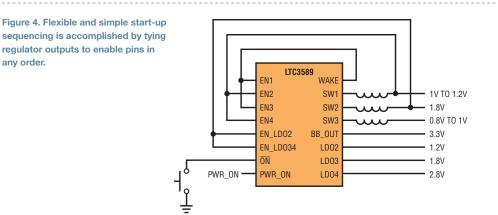

The LTC3589 serves applications processor power needs with eight regulated outputs that support processor core and I/O voltage levels, SRAM, memory, low power standby, other peripheral circuits and system voltage levels. The LTC3589's eight supplies are completely independent, but they can be easily sequenced with simple pin strapping. Likewise, the LTC3589 simplifies overall power system design by integrating a number of important control features, including:

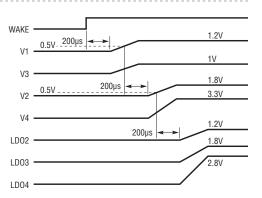

- Flexible pin strap supply sequencing

- I<sup>2</sup>C control of all major regulator functions

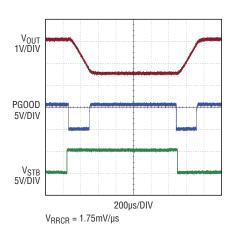

- Dynamic voltage scaling with selectable ramp rate

- IRQ pin and status register error reporting

- Power good status pin and register

- Built-in pushbutton controller to initiate power-on, provide a debounced pushbutton status and force a device hard reset

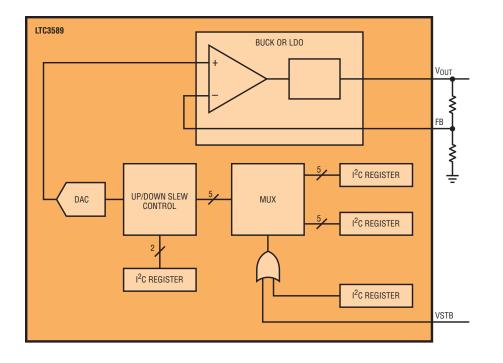

**EIGHT INDEPENDENT VOLTAGE REGULATORS IN A SINGLE IC** While the features built into the LTC3589 certainly aid system design and optimization, it is designed foremost to output eight independent, voltage-regulated outputs. The LTC3589 contains a combination of LDO and switching regulators with output current capabilities from 25mA to 1.6A, with voltage output

Figure 1. Eight power rails take less than 500mm<sup>2</sup> of board real estate.

levels from less than 1V to 5V. Four of the outputs feature  $I^2C$  -controlled DAC references for dynamic voltage scaling.