# L6208

PRELIMINARY DATA

## FULLY INTEGRATED STEPPER MOTOR DRIVER

- OPERATING SUPPLY VOLTAGE FROM 8 TO 52V

- 5.6A PEAK CURRENT (2.8A DC)

- R<sub>DS(ON)</sub> 0.3Ω TYP. VALUE @ T<sub>j</sub> = 25 °C

- BUILT-IN DECODING LOGIC

- BUILT-IN CONSTANT OFF-TIME PWM CURRENT CONTROL

- FAST/SLOW DECAY MODE SELECTION

- HIGH SIDE OVER CURRENT PROTECTION 5.6A TYP.

- CROSS CONDUCTION PROTECTION

- THERMAL SHUTDOWN

- OPERATING FREQUENCY UP TO 100KHz

- INTRINSIC FAST FREE WHEELING DIODES

- UNDER VOLTAGE LOCKOUT

#### TYPICAL APPLICATIONS

BIPOLAR STEPPER MOTOR

#### DESCRIPTION

The L6208 is a fully integrated stepper motor driver manufactured with multipower BCD technology,

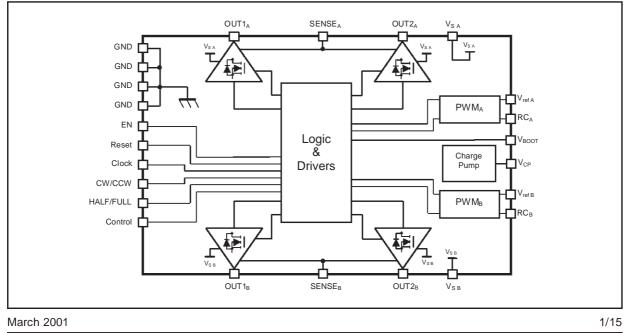

#### **BLOCK DIAGRAM**

which combines isolated DMOS power transistors with CMOS and bipolar circuits on the same chip. The logic inputs are CMOS/TTL and  $\mu$ P compatible. The device also includes all the circuitry needed to drive a stepper motor, that is the constant off time PWM control that performs the chopping current control and the state machine that generates the stepping sequence. Other features are the protection of the high side switches against unsafe over current conditions and the thermal shutdown.

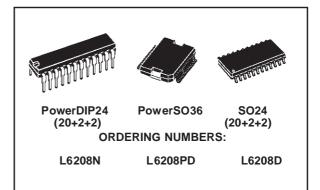

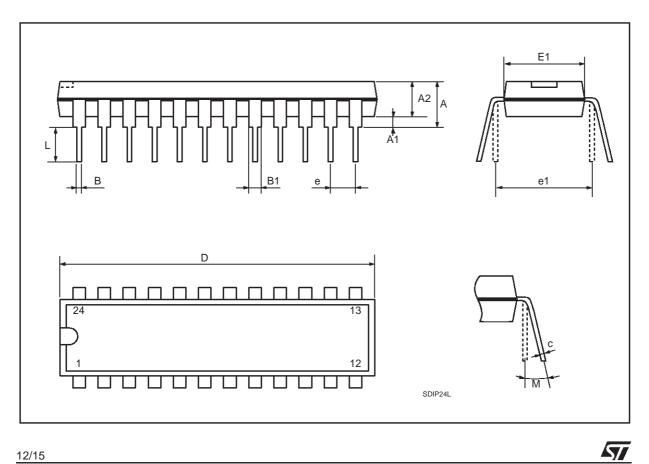

The L6208 is assembled in PowerDIP24(20+2+2), PowerSO36 and SO24(20+2+2) packages.

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

## FUNCTIONAL BLOCK DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                | Parameter                                                                                                                                                                      | Test conditions          | Value               | Unit |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------|------|

| Vs                                    | Supply Voltage                                                                                                                                                                 |                          | 60                  | V    |

| V <sub>IN</sub> ,V <sub>EN</sub>      | Input and Enable Voltage Range                                                                                                                                                 |                          | -0.3 to +7          | V    |

| V <sub>refA</sub> , V <sub>refB</sub> | Voltage Range at V <sub>ref</sub> pins                                                                                                                                         |                          | -0.3 to +7          | V    |

| V <sub>RCA,RCB</sub>                  | Voltage Range at $RC_A$ and $RC_B$ pins                                                                                                                                        |                          | -0.3 to +7          | V    |

| V <sub>SENSE</sub>                    | DC Sensing Voltage Range                                                                                                                                                       |                          | -1 to +4            | V    |

| V <sub>BOOT</sub>                     | Bootstrap Peak Voltage                                                                                                                                                         |                          | V <sub>S</sub> + 10 | V    |

| I <sub>S(peak)</sub>                  | Pulsed Supply Current (for each $V_S$ pin), internally limited by the overcurrent protection                                                                                   | t <sub>PULSE</sub> < 1ms | 7.1                 | A    |

| I <sub>S</sub>                        | DC Supply Current (for each $V_S$ pin)                                                                                                                                         |                          | 2.8                 | A    |

| V <sub>OD</sub>                       | Differential Voltage Between $V_{S A}$ , OUT1 <sub>A</sub> , OUT2 <sub>A</sub> , SENSE <sub>A</sub> and $V_{S B}$ , OUT1 <sub>B</sub> , OUT2 <sub>B</sub> , SENSE <sub>B</sub> |                          | 60                  | V    |

| T <sub>stg</sub> , T <sub>OP</sub>    | Storage and Operating<br>Temperature Range                                                                                                                                     |                          | -40 to 150          | °C   |

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol             | Parameter                                                                                                                                                                      | MIN      | MAX    | Unit   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--------|

| VS                 | Supply Voltage                                                                                                                                                                 | 12       | 52     | V      |

| V <sub>OD</sub>    | Differential Voltage Between $V_{S A}$ , OUT1 <sub>A</sub> , OUT2 <sub>A</sub> , SENSE <sub>A</sub> and $V_{S B}$ , OUT1 <sub>B</sub> , OUT2 <sub>B</sub> , SENSE <sub>B</sub> |          | 52     | V      |

| V <sub>SENSE</sub> | Sensing voltage<br>(pulsed tw <t<sub>rr)<br/>(DC)</t<sub>                                                                                                                      | -6<br>-1 | 6<br>1 | V<br>V |

| V <sub>ref</sub>   | V <sub>ref</sub> Operating Voltage                                                                                                                                             | -0.1     | 5      | V      |

| I <sub>OUT</sub>   | DC Output Current                                                                                                                                                              |          | 2.8    | A      |

| Тј                 | Operating Junction Temperature                                                                                                                                                 | -25      | +125   | °C     |

| f <sub>sw</sub>    | Switching Frequency                                                                                                                                                            |          | 100    | kHz    |

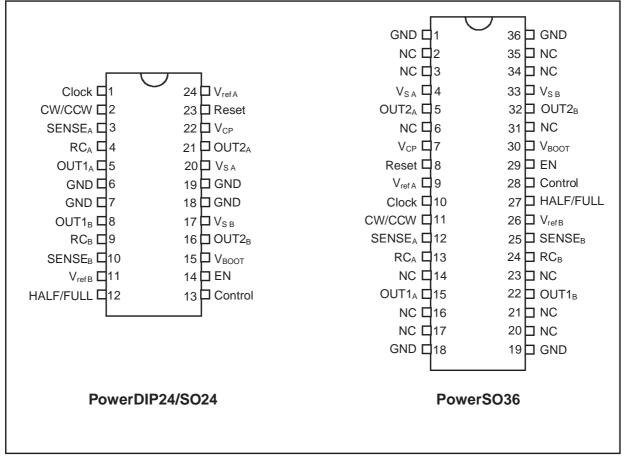

#### PIN CONNECTIONS (Top View)

## L6208

## **PIN DESCRIPTION**

| Name                                   | PowerSO36     | PowerDIP24/<br>SO24 | Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SA</sub>                        | 4             | 20                  | Supply voltage of the bridge A.                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>SB</sub>                        | 33            | 17                  | Supply voltage of the bridge B. Must be connected to $V_{SA}$ .                                                                                                                                                                                                                                                                                                                                               |

| OUT1 <sub>A</sub><br>OUT2 <sub>A</sub> | 15<br>5       | 5<br>21             | Bridge A outputs.                                                                                                                                                                                                                                                                                                                                                                                             |

| OUT1 <sub>B</sub><br>OUT2 <sub>B</sub> | 22<br>32      | 8<br>16             | Bridge B outputs.                                                                                                                                                                                                                                                                                                                                                                                             |

| SENSEA                                 | 12            | 3                   | Sense resistor for the bridge A.                                                                                                                                                                                                                                                                                                                                                                              |

| SENSEB                                 | 25            | 10                  | Sense resistor for the bridge B.                                                                                                                                                                                                                                                                                                                                                                              |

| GND                                    | 1, 18, 19, 36 | 6, 7,<br>18, 19     | Common ground terminals. In Powerdip and SO packages, these pins are also used for heat dissipation toward the PCB.                                                                                                                                                                                                                                                                                           |

| EN                                     | 29            | 14                  | Chip Enable. A Low logic level applied to this pin switches Off all the power DMOSs.                                                                                                                                                                                                                                                                                                                          |

| HALF/FULL                              | 27            | 12                  | Logic input. When high, HALF STEP operation is selected; a Low logic<br>level selects FULL STEP operation.<br>ONE-PHASE-ON FULL STEP MODE ( <i>wave mode</i> ) is obtained by<br>selecting FULL when the state machine is at an <i>even</i> numbered state.<br>TWO-PHASE-ON FULL STEP MODE ( <i>normal mode</i> ) is obtained by<br>selecting FULL when the state machine is at an <i>odd</i> numbered state. |

| Reset                                  | 8             | 23                  | Logic input. A Low logic level restores the <i>home</i> state (state 1) on the state machine.                                                                                                                                                                                                                                                                                                                 |

| Clock                                  | 10            | 1                   | Logic input. Step Clock. The step occurs on the rising edge of this signal.                                                                                                                                                                                                                                                                                                                                   |

| CW/CCW                                 | 11            | 2                   | Logic input. Logic High sets clockwise direction. Logic Low sets counterclockwise direction.                                                                                                                                                                                                                                                                                                                  |

| Control                                | 28            | 13                  | Logic input. Selects chopping style. FAST DECAY is selected with logic Low. A logic High selects SLOW DECAY.                                                                                                                                                                                                                                                                                                  |

| V <sub>ref</sub> A                     | 9             | 24                  | A voltage applied to these pins sets the reference voltage of the sense                                                                                                                                                                                                                                                                                                                                       |

| V <sub>ref B</sub>                     | 26            | 11                  | comparators, determining the output current in PWM current control.                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CP</sub>                        | 7             | 22                  | Bootstrap oscillator. Oscillator output for the external charge pump.                                                                                                                                                                                                                                                                                                                                         |

| V <sub>BOOT</sub>                      | 30            | 15                  | Supply voltage to overdrive the upper DMOSs.                                                                                                                                                                                                                                                                                                                                                                  |

| RC <sub>A</sub>                        | 13            | 4                   | A parallel RC network connected to these pins sets the OFF time of the                                                                                                                                                                                                                                                                                                                                        |

| RC <sub>B</sub>                        | 24            | 9                   | low-side power DMOS of the correspondent bridge. The pulse generator is a monostable triggered by the output of the sense comparator of the bridge ( $t_{OFF} = 0.69$ RC).                                                                                                                                                                                                                                    |

#### THERMAL DATA

| Symbol                 | Description                                                | PowerDIP24 | SO24 | PowerSO36 | Unit |

|------------------------|------------------------------------------------------------|------------|------|-----------|------|

| R <sub>th-j-pins</sub> | MaximumThermal Resistance Junction-Pins                    | 18         | 14   | -         | °C/W |

| R <sub>th-j-case</sub> | Maximum Thermal Resistance Junction-Case                   | -          | -    | 1         | °C/W |

| R <sub>th-j-amb1</sub> | MaximumThermal Resistance Junction-Ambient <sup>(1)</sup>  | 42         | 50   | -         | °C/W |

| R <sub>th-j-amb1</sub> | Maximum Thermal Resistance Junction-Ambient <sup>(2)</sup> | -          | -    | 35        | °C/W |

| R <sub>th-j-amb1</sub> | MaximumThermal Resistance Junction-Ambient <sup>(3)</sup>  | -          | -    | 15        | °C/W |

| R <sub>th-j-amb2</sub> | Maximum Thermal Resistance Junction-Ambient <sup>(4)</sup> | 58         | 77   | 62        | °C/W |

(1) Mounted on a multilayer FR4 PCB with a dissipating copper surface on the bottom side of 6 cm<sup>2</sup> (with a thickness of 35 μm).

(2) Mounted on a multilayer FR4 PCB with a dissipating copper surface on the top side of 6 cm<sup>2</sup> (with a thickness of 35  $\mu$ m). (3) Mounted on a multilayer FR4 PCB with a dissipating copper surface on the top side of 6 cm<sup>2</sup> (with a thickness of 35  $\mu$ m), 16 via holes and a ground layer.

(4) Mounted on a multiplayer PCB without any heatsinking surface on the board..

#### **ELECTRICAL CHARACTERISTICS**

(T<sub>amb</sub> = 25 °C, V<sub>s</sub> = 48V, unless otherwise specified)

| Symbol         | Parameter                    | Parameter Test Conditions                         |     | Тур | Мах | Unit |

|----------------|------------------------------|---------------------------------------------------|-----|-----|-----|------|

| VS             | Supply Voltage               |                                                   | 8   |     | 52  | V    |

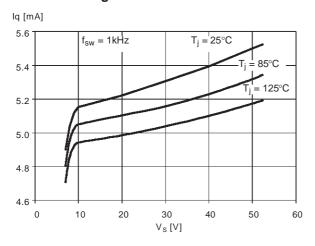

| ۱ <sub>S</sub> | Quiescent Supply Current     | All Bridges OFF; -25°C <t<sub>j &lt;125°C</t<sub> |     | 5.5 | 10  | mA   |

| Тј             | Thermal Shutdown Temperature |                                                   | 150 |     |     | °C   |

## **Output DMOS Transistors**

| I <sub>DSS</sub>    | Leakage Current                | V <sub>S</sub> = 52V   |      | 1    | mA |

|---------------------|--------------------------------|------------------------|------|------|----|

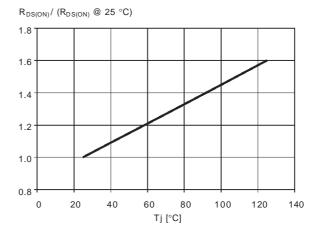

| R <sub>DS(ON)</sub> | High-side Switch ON Resistance | T <sub>j</sub> = 25 °C | 0.34 | 0.4  | Ω  |

|                     |                                | T <sub>j</sub> =125 °C | 0.53 | 0.59 | Ω  |

|                     | Low-side Switch ON Resistance  | T <sub>j</sub> = 25 °C | 0.28 | 0.34 | Ω  |

|                     |                                | T <sub>j</sub> =125 °C | 0.47 | 0.53 | Ω  |

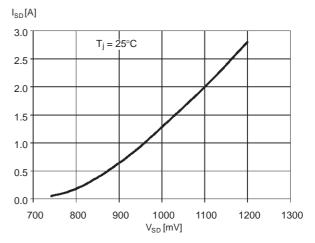

#### **Source Drain Diodes**

| $V_{SD}$        | Forward ON Voltage    | I <sub>SD</sub> = 2.8A, EN = LOW | 1.2 | 1.4 | V  |

|-----------------|-----------------------|----------------------------------|-----|-----|----|

| t <sub>rr</sub> | Reverse Recovery Time | I <sub>f</sub> = 2.8A            | 300 |     | ns |

| t <sub>fr</sub> | Forward Recovery Time |                                  | 200 |     | ns |

#### **Switching Rates**

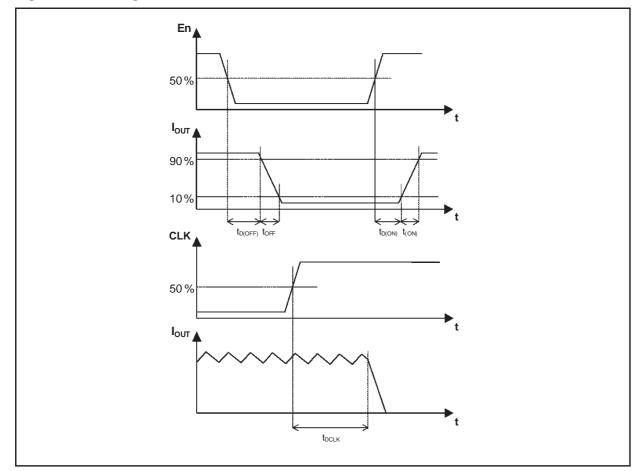

| t <sub>D(on)</sub>  | Enable out Turn ON Delay Time <sup>(5)</sup>        | I <sub>LOAD</sub> =2.8A | 110 | 250 | 400 | ns |

|---------------------|-----------------------------------------------------|-------------------------|-----|-----|-----|----|

| t <sub>ON</sub>     | Output Rise Time <sup>(5)</sup>                     | I <sub>LOAD</sub> =2.8A | 20  | 105 | 300 | ns |

| <sup>t</sup> D(OFF) | Enable to out Turn OFF Delay<br>Time <sup>(5)</sup> | I <sub>LOAD</sub> =2.8A | 240 | 580 | 760 | ns |

| tOFF                | Output Fall Time <sup>(5)</sup>                     | I <sub>LOAD</sub> =2.8A | 20  | 78  | 300 | ns |

| <sup>t</sup> DCLK   | Clock to output delay time <sup>(5)</sup>           | I <sub>LOAD</sub> =2.8A |     | 2   |     | μs |

### ELECTRICAL CHARACTERISTICS (continued)

$(T_{amb} = 25 \text{ °C}, V_s = 48V, \text{ unless otherwise specified})$

| Symbol                      | Parameter                                      | Test Conditions                           | Min                    | Тур    | Мах                    | Unit |

|-----------------------------|------------------------------------------------|-------------------------------------------|------------------------|--------|------------------------|------|

| t <sub>dt</sub>             | Dead Time Protection                           |                                           |                        | 1      |                        | μs   |

| t <sub>blank</sub>          | Internal Blanking Time on SENSE pins           |                                           |                        | 1      | 1.5                    | μs   |

| f <sub>CP</sub>             | Charge pump frequency                          | -25°C <t<sub>j &lt;125°C</t<sub>          |                        | 0.75   | 1                      | MHz  |

| UVLO co                     | np                                             |                                           |                        |        |                        |      |

| V <sub>th(ON)</sub>         | Turn ON threshold                              |                                           | 6.6                    | 7      | 7.4                    | V    |

| $V_{\text{th}(\text{OFF})}$ | Turn OFF threshold                             |                                           | 5.6                    | 6      | 6.4                    | V    |

| Logic Inp                   | ut                                             |                                           |                        |        | <b></b>                |      |

| V <sub>INL</sub>            | Low level logic input voltage                  |                                           | -0.3                   |        | 0.8                    | V    |

| V <sub>INH</sub>            | High level logic input voltage                 |                                           | 2                      |        | 7                      | V    |

| I <sub>INH</sub>            | High level logic input current                 | V <sub>IN, EN</sub> = 5 V                 |                        |        | 70                     | μΑ   |

| I <sub>INL</sub>            | Low level logic input current                  | V <sub>IN, EN</sub> = GND                 |                        |        | -10                    | μA   |

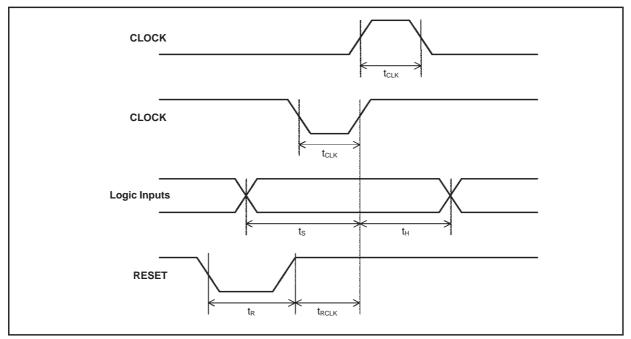

| t <sub>CLK</sub>            | Minimum clock time <sup>(6)</sup>              |                                           |                        | 0.1    | 1                      | μs   |

| t <sub>S</sub>              | Minimum set up time <sup>(6)</sup>             |                                           |                        |        | 1                      | μs   |

| t <sub>H</sub>              | Minimum hold time <sup>(6)</sup>               |                                           |                        |        | 1                      | μs   |

| t <sub>R</sub>              | Minimum reset time <sup>(6)</sup>              |                                           |                        |        | 1                      | μs   |

| t <sub>RCLK</sub>           | Minimum reset to clock delay <sup>(6)</sup>    |                                           |                        |        | 1                      | μs   |

| Over Cur                    | rent Protection                                | I                                         |                        |        |                        |      |

| I <sub>S OVER</sub>         | Input supply over current protection threshold | -25°C <t<sub>j &lt;125°C</t<sub>          | 4                      | 5.6    | 7.1                    | A    |

| V <sub>DIAG</sub>           | Open drain low level output voltage            | I = 4 mA                                  |                        |        | 0.4                    | V    |

| Compara                     | tor and Monostable                             |                                           |                        | I      | <b></b>                | L    |

| I <sub>RCA, RCB</sub>       | Source current at RC pins                      | V <sub>RC</sub> =2.5 V                    | 3                      | 5      |                        | mA   |

| V <sub>ref</sub>            | Input common mode comparator voltage range     |                                           | -0.1                   |        | 5                      | V    |

| V <sub>th</sub>             | Comparator threshold voltage on SENSE pins     | V <sub>ref A, B</sub> = 0.5 V             | V <sub>ref</sub> - 5mV |        | V <sub>ref</sub> + 5mV |      |

| t <sub>prop</sub>           | Turn OFF propagation delay <sup>(7)</sup>      | V <sub>ref A, B</sub> = 0.5 V             | 0.1                    | 0.2    | 0.3                    | μs   |

| toff                        | PWMRecirculation time                          | 20 kΩ < R < 100 kΩ<br>0.1 nF < C < 100 nF | 0.67RC                 | 0.69RC | 0.71RC                 | S    |

| I <sub>bias</sub>           | Input bias current at V <sub>ref</sub> pins    |                                           |                        | 0.2    |                        | μA   |

(5) Resistive load used. See Fig. 1.

(6) See Fig. 2.

(7) Defined as the time between the voltage at the input of the current sense reaching the V<sub>ref</sub> threshold and the lower DMOS switch beginning to turn off. The voltage at SENSE pin is increased instantaneously from V<sub>ref</sub> -10 mV to V<sub>ref</sub> +10 mV.

Figure 1. Switching Rates Definition

Figure 2. Minimum Timing Definition

Figure 3. Typical Quiescent Current vs. Supply Voltage

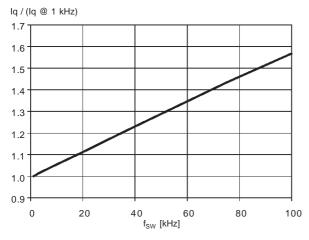

Figure 4. Normalized Typical Quiescent Current vs. Switching Frequency

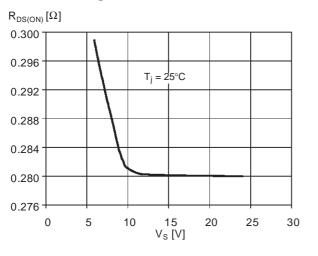

Figure 5. Typical Low-Side R<sub>DS(ON)</sub> vs. Supply Voltage

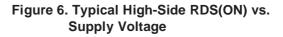

Figure 7. Normalized R<sub>DS(ON)</sub> vs.Junction Temperature (typical value)

Figure 8. Typical Drain-Source Diode Forward ON Characteristic

#### **CIRCUIT DESCRIPTION**

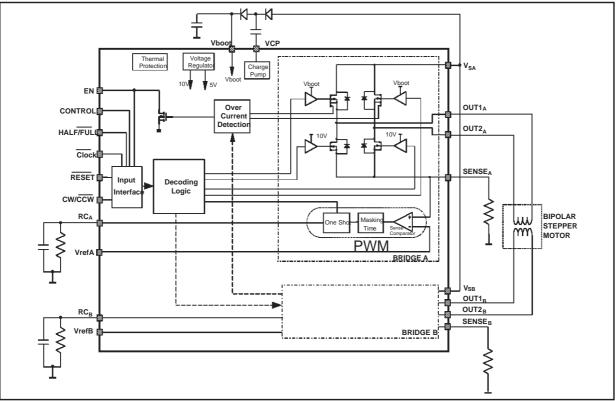

The L6208 is a fully integrated bipolar stepper motor driver with two full bridge having power DMOS with a typical  $R_{DS(ON)}$  of 0.3 $\Omega$  each. All the circuitry to implement the phase generation (decoding logic) is integrated, as well as a constant t<sub>off</sub> PWM control for the current, separately for any of the two winding of the driven motor. The decoding logic generates three different sequences, selected by the HALF/FULL input. These are normal (two phases energized), wave drive (one phase energized) and half-step (alternately one phase/two phases energized).

The constant toff PWM current control consists in a sense comparator and a monostable.

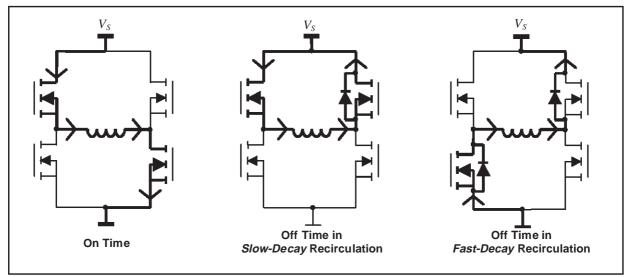

When the current in each phase of the motor reaches the value set by the correspondent  $V_{ef}$  voltage ( $V_{ref}$  /  $R_{SENSE}$ ), it will be forced to decrease for a constant  $\delta_{ff}$  time, set by the RC network applied to the RC<sub>A</sub> and RC<sub>B</sub> pins. If the Control pin is at a High logic level, during the off-time the voltage applied to the motor phase will be approx. 0 V, turning on the high-side MOSFETs of the bridge (slow decay recirculation); if control is Low, instead, the voltage applied to the phase will be reversed, turning off the low side MOSFET that was on and turning on the opposite low-side (fast decay recirculation).

## Figure 9. Decay Modes

Figure 10. PWM Chopping Current Control

A non-dissipative current sensing on the high side power DMOSs, an internal reference and an internal open drain, with a pull down capability of 4mA (typical value), that goes LOW under fault conditions, ensure a protection against short circuit to GND or between two phases of each of the two full bridges. The trip point of this protection is internally set at 5.6 A (typ. value). By using an external R-C on the EN pins, the off time before recovering normal operation conditions after a fault can be easily programmed, by means of the accurate threshold of the logic inputs. Note that protection against short to the supply rail is typically provided by the PWM current control circuitry.

These features make the L6208 a complete bipolar stepper motor driver that outperforms the components currently available on the market.

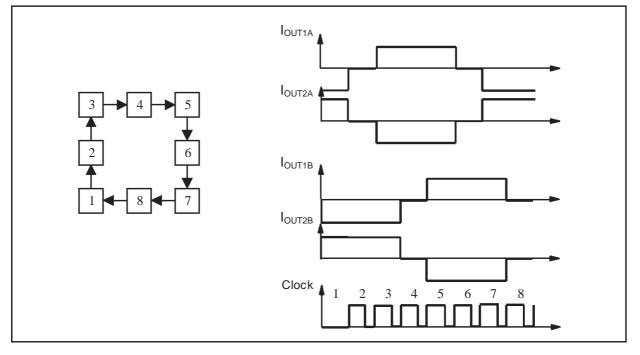

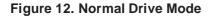

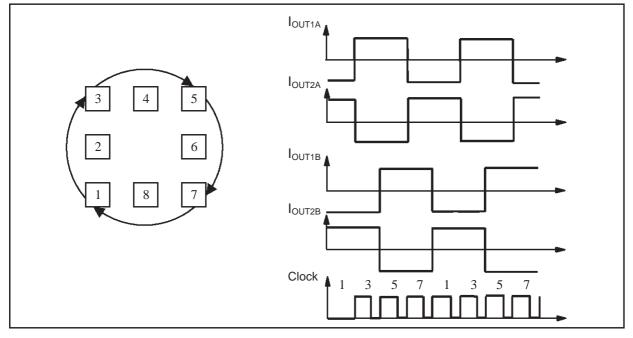

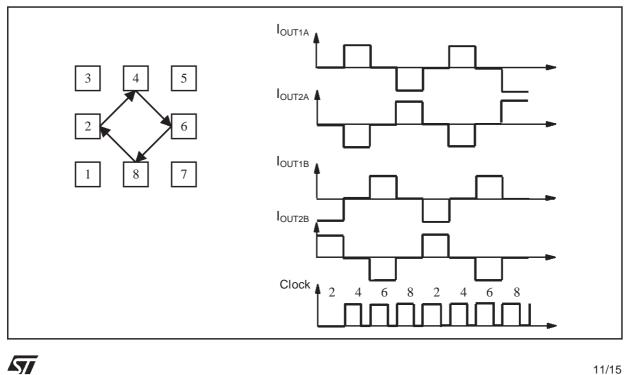

#### MOTOR DRIVING PHASE SEQUENCE

The decoding logic integrated in the L6208 generates the sequences for normal drive, wave drive and half step modes. The state machine sequences and the output currents (neglecting, for simplicity, the PWM control) are shown below, in the case of clockwise rotation. For counterclockwise rotation the sequences are simply reversed. The state machine advances on the rising edge of the Clock signal, and a Low logic level on the Reset input restores the logic to state 1.

#### HALF STEP MODE

Half step mode is selected by a high logic level on the HALF/FULL pin.

#### Figure 11. Half Step Mode

### NORMAL DRIVE MODE (Full-step two-phase-on)

Normal drive mode is selected by a Low level on the HALF/FULL input when the state machine is at an odd numbered state.

## WAVE DRIVE MODE (Full-step one-phase-on)

Wave drive mode is selected by a Low level on the HALF/FULL input when the state machine is at an even numbered state.

#### Figure 13. Wave Drive Mode

| DIM. |       | mm               |       | inch  |       |       |  |

|------|-------|------------------|-------|-------|-------|-------|--|

|      | MIN.  | TYP.             | MAX.  | MIN.  | TYP.  | MAX.  |  |

| A    |       |                  | 4.320 |       |       | 0.170 |  |

| A1   | 0.380 |                  |       | 0.015 |       |       |  |

| A2   |       | 3.300            |       |       | 0.130 |       |  |

| В    | 0.410 | 0.460            | 0.510 | 0.016 | 0.018 | 0.020 |  |

| B1   | 1.400 | 1.520            | 1.650 | 0.055 | 0.060 | 0.065 |  |

| с    | 0.200 | 0.250            | 0.300 | 0.008 | 0.010 | 0.012 |  |

| D    | 31.62 | 31.75            | 31.88 | 1.245 | 1.250 | 1.255 |  |

| E    | 7.620 |                  | 8.260 | 0.300 |       | 0.325 |  |

| е    |       | 2.54             |       |       | 0.100 |       |  |

| E1   | 6.350 | 6.600            | 6.860 | 0.250 | 0.260 | 0.270 |  |

| e1   |       | 7.620            |       |       | 0.300 |       |  |

| L    | 3.180 |                  | 3.430 | 0.125 |       | 0.135 |  |

| М    |       | 0° min, 15° max. |       |       |       |       |  |

12/15

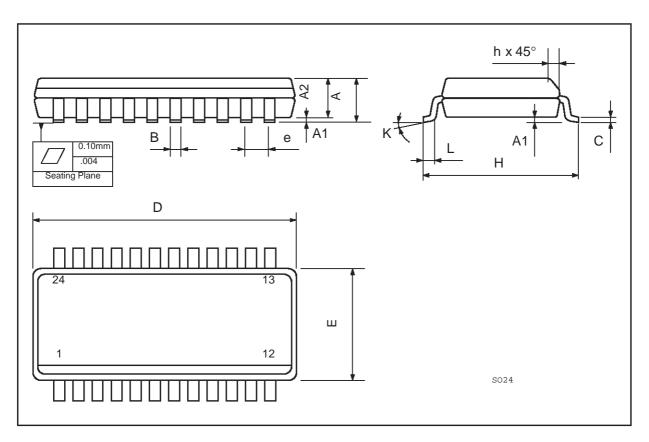

| DIM. | mm                   |      |       | inch  |       |        |  |

|------|----------------------|------|-------|-------|-------|--------|--|

|      | MIN.                 | TYP. | MAX.  | MIN.  | TYP.  | MAX.   |  |

| А    | 2.35                 |      | 2.65  | 0.093 |       | 0.104  |  |

| A1   | 0.10                 |      | 0.30  | 0.004 |       | 0.012  |  |

| A2   |                      |      | 2.55  |       |       | 0.100  |  |

| В    | 0.33                 |      | 0.51  | 0.013 |       | 0.0200 |  |

| С    | 0.23                 |      | 0.32  | 0.009 |       | 0.013  |  |

| D    | 15.20                |      | 15.60 | 0.598 |       | 0.614  |  |

| E    | 7.40                 |      | 7.60  | 0.291 |       | 0.299  |  |

| е    |                      | 1.27 |       |       | 0,050 |        |  |

| н    | 10.0                 |      | 10.65 | 0.394 |       | 0.419  |  |

| h    | 0.25                 |      | 0.75  | 0.010 |       | 0.030  |  |

| k    | 0° (min.), 8° (max.) |      |       |       |       |        |  |

| L    | 0.40                 |      | 1.27  | 0.016 |       | 0.050  |  |

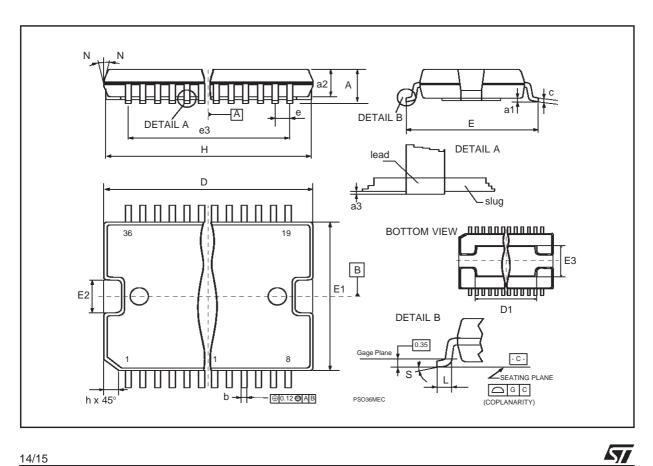

| DIM.   | mm        |       |       | inch  |        |       |  |

|--------|-----------|-------|-------|-------|--------|-------|--|

|        | MIN.      | TYP.  | MAX.  | MIN.  | TYP.   | MAX.  |  |

| Α      |           |       | 3.60  |       |        | 0.141 |  |

| a1     | 0.10      |       | 0.30  | 0.004 |        | 0.012 |  |

| a2     |           |       | 3.30  |       |        | 0.130 |  |

| a3     | 0         |       | 0.10  | 0     |        | 0.004 |  |

| b      | 0.22      |       | 0.38  | 0.008 |        | 0.015 |  |

| С      | 0.23      |       | 0.32  | 0.009 |        | 0.012 |  |

| D (1)  | 15.80     |       | 16.00 | 0.622 |        | 0.630 |  |

| D1     | 9.40      |       | 9.80  | 0.370 |        | 0.385 |  |

| E      | 13.90     |       | 14.50 | 0.547 |        | 0.570 |  |

| е      |           | 0.65  |       |       | 0.0256 |       |  |

| e3     |           | 11.05 |       |       | 0.435  |       |  |

| E1 (1) | 10.90     |       | 11.10 | 0.429 |        | 0.437 |  |

| E2     |           |       | 2.90  |       |        | 0.114 |  |

| E3     | 5.80      |       | 6.20  | 0.228 |        | 0.244 |  |

| E4     | 2.90      |       | 3.20  | 0.114 |        | 0.126 |  |

| G      | 0         |       | 0.10  | 0     |        | 0.004 |  |

| Н      | 15.50     |       | 15.90 | 0.610 |        | 0.626 |  |

| h      |           |       | 1.10  |       |        | 0.043 |  |

| L      | 0.80      |       | 1.10  | 0.031 |        | 0.043 |  |

| N      | 10°(max.) |       |       |       |        |       |  |

| S      | 8 °(max.) |       |       |       |        |       |  |

(1): "D" and "E1" do not include mold flash or protrusions - Mold flash or protrusions shall not exceed 0.15mm (0.006 inch)

| <ul> <li>Critica</li> </ul> | l dimensions are | "a3", | "E" | and ' | 'G". |  |

|-----------------------------|------------------|-------|-----|-------|------|--|

|                             |                  |       |     |       |      |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics ® 2001 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzer Inder - United Kingdom - U.S.A.

http://www.st.com