# AN4677

# Using the SA828/838 PWM IC Family

Application Note

AN4677 - 1.2 January 1997

### OVERVIEW

The SA828/SA838 Pulse Width Modulation ICs incorporate a MOTEL interface which primarily allows them to be controlled by either Intel or Motorola microprocessors and microcontrollers employing an 8-bit multiplexed address/ data bus. However, since the SA8X8 is implemented using fully static logic, the bus can be controlled at lower speeds, making it suitable for use with microcontrollers which have no external bus.

This facility has become increasingly important as the cost of such microcontrollers has fallen and on-chip peripheral integration levels have risen. Microcontrollers such as (but not limited to) the Microchip PIC, Philips 87C75X, Zilog Z86, SGS Thomson ST6 and National Semiconductor COP<sup>†</sup> all feature the maximum number of I/O ports in any given package size by dispensing with external address/ data busses and instead placing modestly sized RAM, EPROM (usually one-time programmable),and in some instances E<sup>2</sup>PROM, on-chip. Additionally, these devices often benefit from on-chip analogue to digital converters, timer/ counters and interrupt handlers.

A corresponding decrease in price is evident in the power electronics which partners the SA8X8 and low-cost microcontroller, with the result that three phase induction motor control is now possible in price-critical applications such as consumer goods. In particular, products such as washing machines, domestic heating pumps and air conditioning units are now candidates for such control schemes, where the benefits of increased motor longevity and improved control may be realised.

#### ADDRESS/DATA BUS SCHEME

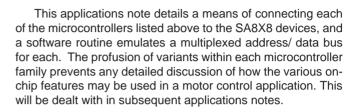

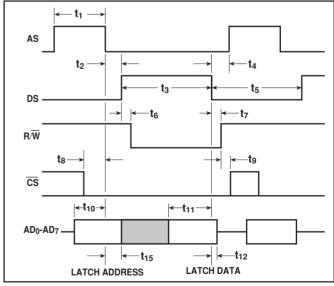

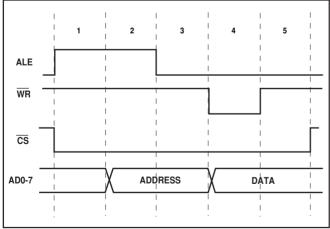

Figs.1a and 1b show the detailed timing diagrams for both Intel and Motorola modes of operation. In each case it is assumed that the SA8X8 device is one of many peripheral devices on the bus and therefore a chip select signal  $(\overline{CS})$  is used to strobe between them.

Clearly, it is irrelevant which of these two forms is emulated by the microcontroller port pins, since both perform exactly the same function. In practice, however, Intel mode has the advantage that the read signal ( $\overline{RD}$ ) remains high for the duration of the <u>cycle</u>- since the SA8X8 is a write-only device. As a result, the WR pin may be tied permanently high.

This leaves three control lines- address latch enable (ALE), write ( $\overline{WR}$ ) and chip select ( $\overline{CS}$ ). If the SA8X8 is the only device on the emulated bus,  $\overline{CS}$  is not required and may be tied permanently low.

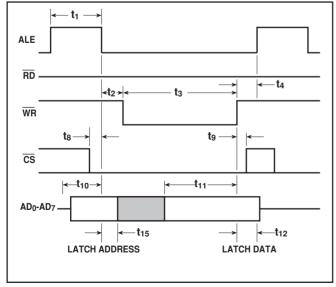

The timing of the various signals may be split into five essential sections:

- 1. CS low, ALE high

- 2. Address set up time

- 3. ALE low, address hold time

- 4. Data setup time,  $\overline{WR}$  low

- 5. Data hold time, WR high, CS high

Fig. 1a Intel bus timing definitions

Fig. 1b Motorola bus timing definitions

| Parameter                       | Symbol          | Min. | Units |

|---------------------------------|-----------------|------|-------|

| ALE high period                 | t <sub>1</sub>  | 70   | ns    |

| Delay time, ALE to WR           | t <sub>2</sub>  | 40   | ns    |

| WR low period                   | t <sub>3</sub>  | 200  | ns    |

| Delay time, WR high to ALE high | t <sub>4</sub>  | 40   | ns    |

| CS setup time                   | t <sub>8</sub>  | 20   | ns    |

| CS hold time                    | t <sub>9</sub>  | 0    | ns    |

| Address setup time              | t <sub>10</sub> | 30   | ns    |

| Address hold time               | t <sub>15</sub> | 30   | ns    |

| Data setup time                 | t <sub>11</sub> | 100  | ns    |

| Data hold time                  | t <sub>12</sub> | 25   | ns    |

Table 1a Intel bus timings at  $V_{DD} = 5V$ ,  $T_{AMB} = +25^{\circ}C$

| Parameter                                  | Symbol          | Min. | Units |

|--------------------------------------------|-----------------|------|-------|

| AS high period                             | t <sub>1</sub>  | 90   | ns    |

| Delay time, as low to DS high              | t <sub>2</sub>  | 40   | ns    |

| DS high period                             | t <sub>3</sub>  | 210  | ns    |

| Delay time, DS low to AS high              | t <sub>4</sub>  | 40   | ns    |

| DS low period                              | t <sub>5</sub>  | 200  | ns    |

| DS high to $R/\overline{W}$ low setup time | t <sub>6</sub>  | 10   | ns    |

| R/W hold time                              | t <sub>7</sub>  | 10   | ns    |

| CS setup time                              | t <sub>8</sub>  | 20   | ns    |

| CS hold time                               | t <sub>9</sub>  | 0    | ns    |

| Address setup time                         | t <sub>10</sub> | 30   | ns    |

| Address hold time                          | t <sub>15</sub> | 30   | ns    |

| Write data setup time                      | t <sub>11</sub> | 110  | ns    |

| Write data hold time                       | t <sub>12</sub> | 30   | ns    |

Table 1b Motorola bus timings at  $V_{DD} = 5V$ ,  $T_{AMB} = +25^{\circ}C$

This may be translated into a flow diagram, as shown in Fig.3:

Fig.3: Address/data bus emulation flow diagram

#### **IMPLEMENTATIONS**

The following sections detail the interconnection diagrams between each of the chosen microcontrollers and the SA8X8 and a subroutine which implements the flow diagram of Fig. 3. For the purposes of direct comparison, the same names have been used for variables and pins in each example. Specific port pins have been selected for each interconnection purely for convention. These may be changed simply by redefining the equates in the source code headers.

Whilst the minimum timings given in Table 1a must be adhered to, in practice this does not present a problem since the instruction cycle time of most microcontrollers is of the order of  $1\mu$ s. The time between any of the five sections listed above is constrained to be at least one instruction but is not subject to a maximum due to the static nature of the SA8X8 MOTEL interface.

The timing diagram may be redrawn as shown in Fig.2. Note that ALE is permitted to go high at any time, provided that t8 (chip select setup) and t4 (delay from  $\overline{WR}$  high to  $\overline{CS}$  low) times are adhered to. Hence, chip select may be exerted at the same time as ALE goes high, so long as  $\overline{WR}$  from a previous instruction goes high at least t4 before this. In fact this is guaranteed due to period 5 in Fig.2. Similarly, period 5 ensures that the t9 (chip select hold) period is adhered to.

Note that there is no necessity to place the address/data lines into a quiescent state after  $\overline{WR}$  becomes inactive since the next instruction will set up the address before the ALE low-going edge. This is guaranteed to occur more than a t12 period following the  $\overline{WR}$  rising edge by virtue of periods 1 and 5 in Fig.2.

Fig.2: Address/data bus timing diagram (Intel Mode)

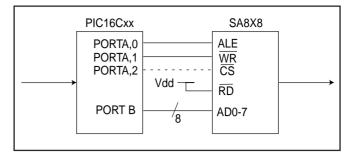

### **1. MICROCHIP PIC SERIES.**

The port pins of the PIC microcontrollers are bi-directional and must be set up as inputs or outputs in the first few lines of code. When defined as an output each port pin is capable of sourcing or sinking 25mA. It is therefore very important that an input cannot be inadvertently redefined as an output since this could cause contention and possibly destroy the device. For this reason the port initialisation routine has been made a subroutine and should be called regularly from the body of the code.

Fig.4: Microchip PIC16CXX interconnection diagram

| ;**********                                                                                                                                                  |                                                                                                              |                                                                                                                           |                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ;BYTE EQUATE                                                                                                                                                 |                                                                                                              | *******                                                                                                                   | *****                                                                                                                                                                      |

| , PORT A                                                                                                                                                     |                                                                                                              | EOU 5                                                                                                                     |                                                                                                                                                                            |

| PORT_P                                                                                                                                                       |                                                                                                              | EQU 5                                                                                                                     |                                                                                                                                                                            |

| ADDRES                                                                                                                                                       |                                                                                                              | ~                                                                                                                         | ; ADDRESS AND DATA REGISTERS                                                                                                                                               |

|                                                                                                                                                              | 55                                                                                                           | ~                                                                                                                         |                                                                                                                                                                            |

| DATA                                                                                                                                                         |                                                                                                              | EQU 1                                                                                                                     | 11                                                                                                                                                                         |

| ; * * * * * * * * * * *                                                                                                                                      | * * * * * * * * * * * *                                                                                      | ******                                                                                                                    | *************                                                                                                                                                              |

| ;BIT EQUATES                                                                                                                                                 |                                                                                                              |                                                                                                                           |                                                                                                                                                                            |

| ;********                                                                                                                                                    |                                                                                                              | *******                                                                                                                   | ***************************************                                                                                                                                    |

| ALE                                                                                                                                                          | EQU                                                                                                          | 0                                                                                                                         | ;PORT_A BIT 0= ALE                                                                                                                                                         |

| WRB                                                                                                                                                          | EQU                                                                                                          | 1                                                                                                                         | ;PORT_A BIT 1= WRB                                                                                                                                                         |

| CSB                                                                                                                                                          | EQU                                                                                                          | 2                                                                                                                         | ;PORT_A BIT 2= CSB                                                                                                                                                         |

| ******                                                                                                                                                       | * * * * * * * * * * * *                                                                                      | * * * * * * * * *                                                                                                         | *****                                                                                                                                                                      |

| ,<br>port_initiai                                                                                                                                            |                                                                                                              |                                                                                                                           | SETS UP QUIESCENT STATE OF PORTS. CALL                                                                                                                                     |

|                                                                                                                                                              |                                                                                                              | ;                                                                                                                         | DURING INITIALISATION ONLY                                                                                                                                                 |

| ; * * * * * * * * * * *                                                                                                                                      | * * * * * * * * * * * *                                                                                      | * * * * * * * * *                                                                                                         | ***************************************                                                                                                                                    |

| BSF                                                                                                                                                          | PORT_                                                                                                        | A,CSB                                                                                                                     | ¿QUIESCENT IS CSB HIGH, WRB HIGH                                                                                                                                           |

| BCF                                                                                                                                                          | PORT                                                                                                         |                                                                                                                           | ; AND ALE LOW.                                                                                                                                                             |

| BSF                                                                                                                                                          | PORT_                                                                                                        |                                                                                                                           |                                                                                                                                                                            |

| MOVLW                                                                                                                                                        | 0FFH                                                                                                         | ,                                                                                                                         |                                                                                                                                                                            |

| MOVEW                                                                                                                                                        | PORT_                                                                                                        | в                                                                                                                         |                                                                                                                                                                            |

| RETLW                                                                                                                                                        |                                                                                                              | ىر                                                                                                                        |                                                                                                                                                                            |

| REILW                                                                                                                                                        | 00H                                                                                                          |                                                                                                                           |                                                                                                                                                                            |

|                                                                                                                                                              |                                                                                                              |                                                                                                                           |                                                                                                                                                                            |

| ; * * * * * * * * * * * *                                                                                                                                    | * * * * * * * * * * * *                                                                                      | *******                                                                                                                   | ******                                                                                                                                                                     |

|                                                                                                                                                              |                                                                                                              |                                                                                                                           |                                                                                                                                                                            |

| ;**********<br>PORT_DEFINI:                                                                                                                                  |                                                                                                              | ;                                                                                                                         | SETS UP I/O PORTS AS INPUTS OR OUTPUTS                                                                                                                                     |

|                                                                                                                                                              |                                                                                                              | : ;                                                                                                                       | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND                                                                                                    |

|                                                                                                                                                              |                                                                                                              | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;                                                                                   | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM                                                                  |

| PORT_DEFINI                                                                                                                                                  | FION_ROUTINE                                                                                                 | ;<br>;<br>;                                                                                                               | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION                                         |

| ;*********                                                                                                                                                   | FION_ROUTINE                                                                                                 | ;<br>;<br>;<br>;<br>;<br>;                                                                                                | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION                                         |

| PORT_DEFINI                                                                                                                                                  | FION_ROUTINE<br>************<br>XXXXX                                                                        | ;;<br>;;<br>;;<br>;**********                                                                                             | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION                                         |

| ;*********                                                                                                                                                   | FION_ROUTINE                                                                                                 | ;;<br>;;<br>;;<br>;**********                                                                                             | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION                                         |

| PORT_DEFINI:<br>;***********                                                                                                                                 | FION_ROUTINE<br>************<br>XXXXX                                                                        | ;;<br>;;<br>;;<br>;**********                                                                                             | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION                                         |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS                                                                                                                 | TION_ROUTINE                                                                                                 | ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;                               | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>;3 LSB'S OF PORT_A ARE O/PS          |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW                                                                                                        | TION_ROUTINE                                                                                                 | ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;                               | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>;3 LSB'S OF PORT_A ARE O/PS          |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW                                                                                       | TION_ROUTINE<br>**************<br>XXXXX<br>PORT_<br>00H<br>PORT_<br>00H                                      | : ;<br>;<br>;<br>;<br>;<br>000B<br>A<br>B                                                                                 | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW<br>;**********                                                                        | TION_ROUTINE<br>************<br>XXXXX<br>PORT_<br>00H<br>PORT_<br>00H                                        | : ;<br>;<br>;<br>;<br>000B<br>A<br>B                                                                                      | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW                                                                                       | TION_ROUTINE<br>************<br>XXXXX<br>PORT_<br>00H<br>PORT_<br>00H                                        | : ;<br>;<br>;<br>;<br>000B<br>A<br>B<br>*********                                                                         | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********************************                                                                                                          | TION_ROUTINE<br>************<br>XXXXX<br>PORT_<br>00H<br>PORT_<br>00H                                        | : ;<br>;<br>;<br>;<br>000B<br>A<br>B<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW<br>;************                                                                      | FION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>000B<br>A<br>B<br>;<br>;;                                                                                | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW<br>;***********<br>BUS_EMULATON<br>;************<br>BCF                               | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>000B<br>A<br>B<br>********<br>;<br>;<br>;<br>A,CSB                                                       | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| <pre>, ************************************</pre>                                                                                                            | FION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>000B<br>A<br>B<br>********<br>;<br>;<br>;<br>A,CSB                                                       | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW<br>;***********<br>BUS_EMULATON<br>;************<br>BCF                               | TION_ROUTINE<br>*************<br>VXXXX<br>PORT_<br>00H<br>PORT_<br>00H<br>********************************** | ; ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;                             | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********************************                                                                                                          | TION_ROUTINE<br>************<br>VXXXX<br>PORT_<br>00H<br>PORT_<br>00H<br>**********************************  | : ;<br>;<br>;<br>0000B<br>A<br>B<br>********<br>;<br>;<br>A, CSB<br>A, ALE<br>SS, W                                       | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW<br>;************************************                                              | TION_ROUTINE<br>*************<br>VXXXX<br>PORT_<br>00H<br>PORT_<br>00H<br>********************************** | : ;<br>;<br>;<br>0000B<br>A<br>B<br>********<br>;<br>;<br>A, CSB<br>A, ALE<br>SS, W                                       | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI<br>;***********************************                                                                                                          | TION_ROUTINE<br>************<br>VXXXX<br>PORT_<br>00H<br>PORT_<br>00H<br>**********************************  | : ;<br>;<br>;<br>000B<br>A<br>B<br>********<br>;<br>;<br>A,CSB<br>A,ALE<br>SS,W<br>B                                      | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI:<br>;************************************                                                                                                        | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>000B<br>A<br>B<br>B<br>**********<br>A<br>A<br>CSB<br>A,ALE<br>SS,W<br>B<br>A,ALE                        | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI:<br>;************************************                                                                                                        | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>000B<br>A<br>B<br>B<br>**********<br>A<br>A<br>CSB<br>A,ALE<br>SS,W<br>B<br>A,ALE                        | SECTION 3. ALE LOW<br>SECTION 4. WRB LOW AND                                                                                                                               |

| PORT_DEFINI<br>;***********<br>MOVLW<br>TRIS<br>MOVLW<br>TRIS<br>RETLW<br>;***********<br>BUS_EMULATON<br>;***********<br>BCF<br>BSF<br>MOVF<br>MOVWF<br>BCF | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>0008<br>A<br>B<br>********<br>A,CSB<br>A,ALE<br>SS,W<br>B<br>A,ALE<br>A,ALE<br>A,WRB                     | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI:<br>;************************************                                                                                                        | TION_ROUTINE<br>************************************                                                         | ;;;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;;<br>;                                               | SECTION 3. ALE LOW<br>SECTION 4. WRB LOW AND                                                                                                                               |

| PORT_DEFINI:<br>;************************************                                                                                                        | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;                             | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

| PORT_DEFINI:<br>;************************************                                                                                                        | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;                             | SECTION 3. ALE LOW<br>SECTION 4. WRB LOW AND                                                                                                                               |

| PORT_DEFINI:<br>;************************************                                                                                                        | TION_ROUTINE<br>************************************                                                         | : ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;                             | SETS UP I/O PORTS AS INPUTS OR OUTPUTS<br>CALL DURING INITILISATION AND<br>REGULARLY FROM BODY OF PROGRAM<br>TO PREVENT CONTENTION<br>************************************ |

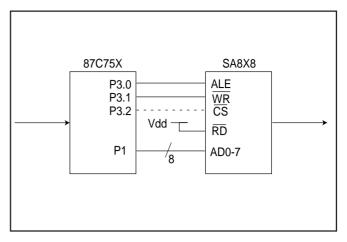

### 2. PHILIPS 87C75X SERIES

The port pins on these devices, like all MCS51 derivatives, are "quasi bi-directional". This means that they have weak pullup resistors and a single transistor which when turned on will take the output low. Therefore, to configure such a port as a high output, ensure that the transistor is off and to configure as a low output ensure that it is on. To use this port as an input, first ensure that the transistor is off and then read the pin in the usual way. Because the pull-up resistor is weak the pin may pulled low externally.

Consequently, this range of microcontrollers does not have direction registers. The only requirement is to ensure that the transistor is off when using any given port as an input. (NOTE: Some ports are open-drain only. Please check when reconfiguring functions to different port pins than those specified).

Fig.5: Philips 87C75X interconnection diagram

| ; HIT EQUATES<br>; HIT EQUATES<br>; ALE BIT P3.0 ; PORT 3 BIT 0= ALE<br>WRB BIT P3.1 ; PORT 3 BIT 1= WRB<br>CSB BIT P3.2 ; PORT 3 BIT 2= CSB<br>; CSB ; PORT_INITIALISE ; SETS UP QUIESCENT STATE OF PORTS.<br>; DURING INITIALISATION ONLY<br>; CLR ALE ; AND ALE LOW.<br>SETB WRB<br>MOV P1, #0FFH<br>RET<br>; MOV P1, #0FFH<br>RET<br>; MOV P1, ADDRESS AND DATA WORDS<br>; CLR CSB ; SECTION 1. ALE HIGH, C<br>SETB ALE<br>MOV P1, ADDRESS ; SECTION 2. SET UP ADDR<br>CLR ALE ; SECTION 3. ALE LOW                                             | ITERNAL RAM EQUATES                     |                             |                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------|-----------------------------------------|

| DATA DATA 09H ;PLACED ABOVE REG BANK<br>;<br>HIT EQUATES<br>;<br>ALE BIT P3.0 ;PORT 3 BIT 0= ALE<br>WRB BIT P3.1 ;PORT 3 BIT 1= WRB<br>CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br>;<br>PORT_INITIALISE ;SETS UP QUIESCENT STATE OF PORTS.<br>;DURING INITIALISATION ONLY<br>;<br>SETB CSB ;QUIESCENT IS CSB HIGH,<br>CLR ALE ;AND ALE LOW.<br>SETB WRB<br>MOV P1, #OFFH<br>RET<br>;<br>CLR CSB ;IMPORT ADDRESS AND DATA WORDS<br>;<br>CLR CSB ;SECTION 1. ALE HIGH, C<br>SETB ALE<br>MOV P1, ADDRESS ;SECTION 2. SET UP ADDR<br>CLR ALE ;SECTION 3. ALE LOW | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ; HIT EQUATES<br>; HIT EQUATES<br>; ALE BIT P3.0 ; PORT 3 BIT 0= ALE<br>WRB BIT P3.1 ; PORT 3 BIT 1= WRB<br>CSB BIT P3.2 ; PORT 3 BIT 2= CSB<br>; CSB ; PORT_INITIALISE ; SETS UP QUIESCENT STATE OF PORTS.<br>; DURING INITIALISATION ONLY<br>; CLR ALE ; AND ALE LOW.<br>SETB WRB<br>MOV P1, #0FFH<br>RET<br>; CLR CSB ; SECTION 1-5 OF FIGURE<br>; IMPORT ADDRESS AND DATA WORDS<br>;<br>CLR CSB ; SECTION 1. ALE HIGH, C<br>SETB ALE<br>MOV P1, ADDRESS ; SECTION 2. SET UP ADDE<br>CLR ALE ; SECTION 3. ALE LOW                                | ADDRESS                                 | DATA 08H                    | ;ADDRESS AND DATA REGISTERS             |

| <pre>;HIT EQUATES<br/>;<br/>ALE BIT P3.0 ;PORT 3 BIT 0= ALE<br/>WRB BIT P3.1 ;PORT 3 BIT 1= WRB<br/>CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br/>;<br/>;<br/>*********************************</pre>                                                                                                                                                                                                                                                                                                                                                         | DATA                                    | DATA 09H                    | ; PLACED ABOVE REG BANK 0               |

| ALE BIT P3.0 ;PORT 3 BIT 0= ALE<br>WRB BIT P3.1 ;PORT 3 BIT 1= WRB<br>CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br>;<br>PORT_INITIALISE ;SETS UP QUIESCENT STATE OF PORTS.<br>;DURING INITIALISATION ONLY<br>;<br>SETB CSB ;QUIESCENT IS CSB HIGH,<br>CLR ALE ;AND ALE LOW.<br>SETB WRB<br>MOV P1,#0FFH<br>RET<br>;<br>CLR CSB ;SECTIONS 1-5 OF FIGURE<br>;IMPORT ADDRESS AND DATA WORDS<br>;<br>CLR CSB ;SECTION 1. ALE HIGH, C<br>SETB ALE<br>MOV P1,ADDRESS ;SECTION 2. SET UP ADDR<br>CLR ALE ;SECTION 3. ALE LOW                                         | *****                                   | * * * * * * * * * * * * * * | ******                                  |

| ALE BIT P3.0 ;PORT 3 BIT 0= ALE<br>WRB BIT P3.1 ;PORT 3 BIT 1= WRB<br>CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                      | T EQUATES                               |                             |                                         |

| WRB BIT P3.1 ;PORT 3 BIT 1= WRB<br>CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                         | * * * * * * * * * * * * * * * * * * * * | *****                       | * * * * * * * * * * * * * * * * * * * * |

| CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ALE                                     | BIT P3.0                    | ;PORT 3 BIT 0= ALE                      |

| CSB BIT P3.2 ;PORT 3 BIT 2= CSB<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | WRB                                     | BIT P3.1                    | ;PORT 3 BIT 1= WRB                      |

| PORT_INITIALISE ;SETS UP QUIESCENT STATE OF PORTS.<br>;DURING INITIALISATION ONLY<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                          | CSB                                     |                             |                                         |

| ;*************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * | ******                                  |

| ;*************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | T_INITIALISE                            | ;SETS                       | UP QUIESCENT STATE OF PORTS. CALL       |

| .   SETB   CSB   ;QUIESCENT IS CSB HIGH,     CLR   ALE   ;AND ALE LOW.     SETB   WRB     MOV   P1,#0FFH     RET   ;IMPLEMENTS SECTIONS 1-5 OF FIGURE     ;UPORT ADDRESS AND DATA WORDS     ;************************************                                                                                                                                                                                                                                                                                                                   |                                         | ;DURIN                      | IG INITIALISATION ONLY                  |

| CLR ALE ;AND ALE LOW.<br>SETB WRB<br>MOV P1,#0FFH<br>RET<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                   | * * * * * * * * * * * * * * * * * * * * | *****                       | * * * * * * * * * * * * * * * * * * * * |

| CLR ALE ;AND ALE LOW.<br>SETB WRB<br>MOV P1,#0FFH<br>RET<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SETB                                    | CSB                         | ;QUIESCENT IS CSB HIGH, WRB HIGH        |

| SETB WRB<br>MOV P1,#0FFH<br>RET<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLR                                     | ALE                         |                                         |

| RET<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SETB                                    | WRB                         |                                         |

| RET<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |                             |                                         |

| BUS_EMULATOR ;IMPLEMENTS SECTIONS 1-5 OF FIGURE<br>;IMPORT ADDRESS AND DATA WORDS<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | 1 1 / 11 01 1 11            |                                         |

| BUS_EMULATOR ;IMPLEMENTS SECTIONS 1-5 OF FIGURE<br>;IMPORT ADDRESS AND DATA WORDS<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |                             |                                         |

| ; IMPORT ADDRESS AND DATA WORDS<br>;************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | * * * * * * * * * * * * * * * * * * * * | *****                       | * * * * * * * * * * * * * * * * * * * * |

| ;*************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _EMULATOR                               | ;IMPLE                      | MENTS SECTIONS 1-5 OF FIGURE 3          |

| CLR CSB ;SECTION 1. ALE HIGH, C<br>SETB ALE<br>MOV P1,ADDRESS ;SECTION 2. SET UP ADDF<br>CLR ALE ;SECTION 3. ALE LOW                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | ;IMPOR                      | T ADDRESS AND DATA WORDS                |

| SETBALEMOVP1,ADDRESSCLRALE, SECTION 3. ALE LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | * * * * * * * * * * * * * * * * * * * * | *****                       | * * * * * * * * * * * * * * * * * * * * |

| MOV P1,ADDRESS ;SECTION 2. SET UP ADDR<br>CLR ALE ;SECTION 3. ALE LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CLR                                     | CSB                         | ;SECTION 1. ALE HIGH, CSB LOW           |

| CLR ALE ;SECTION 3. ALE LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SETB                                    | ALE                         |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MOV                                     | P1,ADDRESS                  | ;SECTION 2. SET UP ADDRESS              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CLR                                     | ALE                         | ;SECTION 3. ALE LOW                     |

| CLR WRB SECTION 4. WRB LOW AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLR                                     | WRB                         | ;SECTION 4. WRB LOW AND                 |

| MOV P1,DATA ;SETUP DATA TO AD0-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MOV                                     | P1,DATA                     | ;SETUP DATA TO AD0-7                    |

| SETB WRB ;SECTION 5. WRB & CSB H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SETB                                    | WRB                         | ;SECTION 5. WRB & CSB HIGH              |

| SETB CSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SETB                                    | CSB                         |                                         |

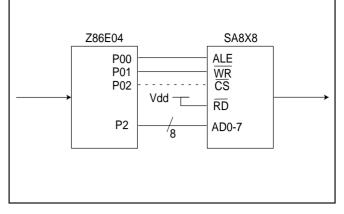

#### 3. ZILOG Z86C/Z86E SERIES

The port pins on these devices are variously configured as I/O, inputs or outputs. Taking the One-Time-Programmable Z86E04 as an example, P0 is a three bit I/O port, P1 is a three bit input only port and P2 is an eight bit I/O port. For simplicity the following example uses P2 as the address/ data bus and P0 as the control bus ( $\overline{CS}$ ,  $\overline{WR}$  and ALE).

The instruction set makes no provisions for 'bit set' and 'bit clear' instructions to toggle port pins high and low. However, a read-modify-write architecture allows bit setting, clearing and toggling using OR, AND and XOR functions respectively. Since the initial read operation reads the state of the port pins themselves, rather than the port data registers, there is a risk of erroneous operation if the two states do not agree. This may occur particularly if the ports are defined to be open-drain and there is no external means for pulling the pin high. For this reason all the port pins in the listings below have been set to push-pull mode. (An additional safeguard consists of keeping an 'image' of the port data registers after each change).

In this particular case, however, using P0 as the three-bit control bus means that it is never necessary to set or clear individual port pins. It is adequate simply to write to all three pins simultaneously since they are all controlled exclusively inside the BUS\_EMULATOR routine.

Fig.6: Zilog Z86 interconnection diagram

| INTERNAL RAM EQUAT                    | ,                                   | . U<br>************                                        |

|---------------------------------------|-------------------------------------|------------------------------------------------------------|

| ADDRESS                               | .equ 04H                            | ; ADDRESS AND DATA REGISTERS                               |

| address                               | .equ r4                             | PLACED ABOVE PORTS IN REG BANKO                            |

| DATA                                  | .equ 05H                            | FIACED ABOVE FORIS IN REG BANKO                            |

| data                                  | .equ r5                             |                                                            |

| * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * | *******                                                    |

| ORT_INITIALISE                        | ;SETS (                             | JP QUIESCENT STATE OF PORTS.                               |

| * * * * * * * * * * * * * * * * * *   | *****                               | ***********                                                |

| LD                                    | P0,#110B                            | ;CS/ HIGH, WR/ HIGH, ALE LOW                               |

| LD                                    | P2,#%FF                             | ;SET ADDRESS/DATA BUS TO QUIESCENT                         |

| LD                                    | P2M,#%00                            | ; PORT2 ALL OUTPUTS                                        |

| LD                                    | P3M,#%01                            | ;P3 I/PS DIGITAL, P2 OP/S PUSH/PUL                         |

| LD                                    | P01M,#%04                           | ; PORTO ALL OUTPUTS                                        |

| RET                                   |                                     |                                                            |

| US_EMULATOR                           | ; IMPORT                            | MENTS SECTIONS 1-5 OF FIGURE 3<br>F ADDRESS AND DATA WORDS |

| LD                                    | P0,#011B                            |                                                            |

| MOV                                   | P2, ADDRESS                         | ;SECTION 2. SET UP ADDRESS                                 |

| LD                                    | P0,#010B                            | ;SECTION 3. ALE LOW                                        |

| LD                                    | P0,#000B                            | ;SECTION 4. WRB LOW AND                                    |

| MOV                                   | P2,DATA                             | ;SETUP DATA TO AD0-7                                       |

| LD<br>RET                             | P0,#110B                            | ;SECTION 5. WRB & CSB HIGH ;RETURN                         |

|                                       |                                     |                                                            |

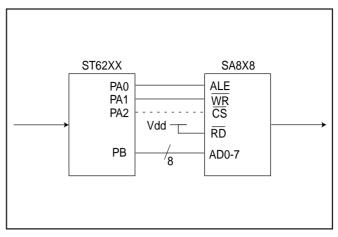

## 4. SGS THOMSON ST6 SERIES.

The port pins of these devices are particularly versatileallowing virtually any pin to be input, output (push-pull or open drain, internal pull-up optional), interrupts and in some cases analogue to digital converter inputs. For the reasons given in Section 3, all outputs have been defined as push-pull in this instance.

Three registers exist for each port: Option Register (ORx), Data Direction Register (DDRx) and Data Register (DRx). Individual bits of the DDR register defines whether the port is input (0) or output (1), whilst each bit of the OP register defines whether the pin is push-pull or open-drain (when configured as an output).

For a push-pull output both the DDR and OR bits need to be high. The DR register then holds the output data. For the purposes of this example, Port A has been used as the control bus and Port B as the address/ data bus.

Fig.7: SGS Thomson ST62 interconnection diagram

| **************                                   |                                                                                           | 0                                                                                                                                     |

|--------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                | .def 84H                                                                                  | **************************************                                                                                                |

| ADDRESS                                          | .def 85H                                                                                  | ADDRESS AND DATA REGISTERS                                                                                                            |

| DATA                                             | .dei 85H                                                                                  |                                                                                                                                       |

| ALE                                              | .equ 0                                                                                    | ;PORT B BITS EQUATES                                                                                                                  |

| WRB                                              | .equ 1                                                                                    |                                                                                                                                       |

| ALE                                              | .equ 2                                                                                    |                                                                                                                                       |

| ****                                             | * * * * * * * * * * * * * * * * * * * *                                                   | ****                                                                                                                                  |

| ,<br>PORT INITIALISE                             | SETS II                                                                                   | QUIESCENT STATE OF PORTS.                                                                                                             |

|                                                  |                                                                                           | *****                                                                                                                                 |

| , LDI                                            | DRB, OFFH                                                                                 | ;SET ADDRESS/DATA BUS TO QUIESCE                                                                                                      |

|                                                  |                                                                                           | ~ ~                                                                                                                                   |

| LDI                                              | DRA,XIIUB                                                                                 | ;CS/ HIGH, WR/ HIGH, ALE LOW                                                                                                          |

| LDI                                              | ORA,#0FH                                                                                  | ; PORTA AND B SET TO PUSH-PULL                                                                                                        |

| LDI                                              | ORB,#0FFH                                                                                 |                                                                                                                                       |

| LDI                                              | DDRA, #0FH                                                                                | ; PORTA AND B SET TO OUTPUTS                                                                                                          |

| LDI                                              | DDRB,#0FFH                                                                                |                                                                                                                                       |

| RET                                              |                                                                                           |                                                                                                                                       |

|                                                  |                                                                                           |                                                                                                                                       |

| 1                                                |                                                                                           | ***************************************                                                                                               |

| BUS_EMULATOR                                     |                                                                                           | ENTS SECTIONS 1-5 OF FIGURE 3                                                                                                         |

|                                                  |                                                                                           | ADDRESS AND DATA WORDS                                                                                                                |

|                                                  |                                                                                           |                                                                                                                                       |

| ; * * * * * * * * * * * * * * * * * *            | * * * * * * * * * * * * * * * * * * * *                                                   | * * * * * * * * * * * * * * * * * * * *                                                                                               |

| ;*************************************           | CSB, DRA                                                                                  | **************************************                                                                                                |

| 1                                                |                                                                                           |                                                                                                                                       |

| RES                                              | CSB, DRA                                                                                  |                                                                                                                                       |

| ,<br>RES<br>SET<br>LD                            | CSB, DRA<br>ALE, DRA<br>A, ADDRESS                                                        | ;SECTION 1. ALE HIGH, CSB LOW                                                                                                         |

| ,<br>RES<br>SET                                  | CSB, DRA<br>ALE, DRA                                                                      | ;SECTION 1. ALE HIGH, CSB LOW                                                                                                         |

| ,<br>RES<br>SET<br>LD                            | CSB, DRA<br>ALE, DRA<br>A, ADDRESS                                                        | ;SECTION 1. ALE HIGH, CSB LOW                                                                                                         |

| RES<br>SET<br>LD<br>LD                           | CSB,DRA<br>ALE,DRA<br>A,ADDRESS<br>DRB,A                                                  | ;SECTION 1. ALE HIGH, CSE LOW                                                                                                         |

| RES<br>SET<br>LD<br>LD<br>RES                    | CSB, DRA<br>ALE, DRA<br>A, ADDRESS<br>DRB, A<br>ALE, DRA<br>WRB, DRA                      | ;SECTION 1. ALE HIGH, CSE LOW<br>;SECTION 2. SET UP ADDRESS<br>;SECTION 3. ALE LOW<br>;SECTION 4. WRB LOW AND                         |

| RES<br>SET<br>LD<br>LD<br>RES<br>RES<br>LD       | CSB, DRA<br>ALE, DRA<br>A, ADDRESS<br>DRB, A<br>ALE, DRA<br>WRB, DRA<br>A, DATA           | ;SECTION 1. ALE HIGH, CSE LOW<br>;SECTION 2. SET UP ADDRESS<br>;SECTION 3. ALE LOW                                                    |

| RES<br>SET<br>LD<br>LD<br>RES<br>RES             | CSB, DRA<br>ALE, DRA<br>A, ADDRESS<br>DRB, A<br>ALE, DRA<br>WRB, DRA                      | ;SECTION 1. ALE HIGH, CSE LOW<br>;SECTION 2. SET UP ADDRESS<br>;SECTION 3. ALE LOW<br>;SECTION 4. WRB LOW AND                         |

| RES<br>SET<br>LD<br>LD<br>RES<br>RES<br>LD       | CSB, DRA<br>ALE, DRA<br>A, ADDRESS<br>DRB, A<br>ALE, DRA<br>WRB, DRA<br>A, DATA           | ;SECTION 1. ALE HIGH, CSE LOW<br>;SECTION 2. SET UP ADDRESS<br>;SECTION 3. ALE LOW<br>;SECTION 4. WRB LOW AND                         |

| RES<br>SET<br>LD<br>LD<br>RES<br>RES<br>LD<br>LD | CSB, DRA<br>ALE, DRA<br>A, ADDRESS<br>DRB, A<br>ALE, DRA<br>WRB, DRA<br>A, DATA<br>DRB, A | ;SECTION 1. ALE HIGH, CSB LOW<br>;SECTION 2. SET UP ADDRESS<br>;SECTION 3. ALE LOW<br>;SECTION 4. WRB LOW AND<br>;SETUP DATA TO AD0-7 |

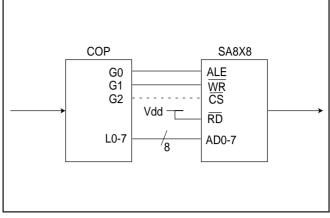

# 5. NATIONAL SEMICONDUCTOR COP SERIES.

The port pins of this range of microcontrollers differ substantially from one to the next. Port L, however, exists on all devices and is a general purpose eight-bit I/O port. In addition Port G exists on all devices although it is of variable length, dependent upon the size (pin-count) of the particular variant. Port L has therefore been adopted as the address/ data port and Port G as the control port.

Two registers exist for each port: Port Configuration (PxC) and Port Data (PxD). Individual bits of the PxC register defines whether the port is input (1) or output (0), whilst each bit of the PxD register defines the output state.

Fig.8: National Semiconductor COP interconnection diagram