## AN1377 APPLICATION NOTE FLEXIBLE DC-DC CONVERTERS FOR EASY INCLUSION IN AN OEM PROJECT

B. Taylor - J. Noe

## 1. INTRODUCTION.

Many OEMs, when they are involved with introducing a new product, have little or no experience of designing in the DC Sourced power supply for such a project. For one reason, or another, they may equally well be reluctant to use an off the shelf product from a specialist supplier. This reluctance could easily stem from the fact their project requires supplies that may not be included within the specialist supplier's catalog. Herein lies the OEM's dilemma. Do they call on the expertise of specialist designers or do they opt for a compromise solution?

One alternative to the OEM's dilemma would be a compromise solution, which utilized one or more linear regulators.

A second alternative would be the adoption of 'solutions' that may be found in certain Vendor's Application Notes – which is not to be recommended.

The purpose of this application note is to address both of the alternative solutions and to demonstrate the real feasibility as to how a little forethought can significantly increase the OEM's capability to design his/ her very own supply and thereby enhance the Added Value of his/her product – while saving themselves the cost of buying in supplies from an outside source or the cost of a specialist designer's expertise.

## 2. THE ADVANTAGES OF SWITCHING REGULATORS OVER LINEAR REGULATORS.

In many instances the input voltage may well be sourced from a battery or other DC source. A linear regulator, which might well be required, by the application, to step the input voltage up to a higher level is not so easy to achieve – if not completely impossible. If that was not all then consider the possibility of Input to Output Galvanic Isolation. A switching regulator will easily accommodate both necessities while a linear regulator solution would require an inverter and rectifier stage – which all add to the cost, and complexity of the solution.

Finally there are the small inconveniences of size, mass, input voltage range and efficiency to consider - with the final two categories being inter-related. In all of the four categories, without exception, the switching regulator is easily superior to the linear regulator. Take for example efficiency... A high-efficiency linear regulator, while being expensive to design and manufacture, would not have a theoretical efficiency greater than 75%. A relatively simple switching regulator, on the other hand, would have to be poorly designed if its efficiency were to fall to that level. Efficiencies of 80%, and greater, are relatively easy to achieve – without becoming prohibitively expensive in their achievement.

Finally there is the matter of cost to consider and it is here that the differences become virtually negligible

- unless the regulator is asked to work over an extremely wide input voltage range (say 4:1) and have input to output isolation; when cost will now be seen to definitely favor the switching regulator. It is this consideration, which is found to be the driving force in the creation of this application note.

## 3. DESIGN RULES FOR SWITCHING REGULATORS.

Before one even begins to consider the Mathematics (and the Physics) of the design process, it is essential for certain extremely specific criteria to be laid down. Usually a part of the specification, these are:

## 1. Input Voltage Range - Absolute Minimum to Absolute Maximum.

This is an absolute necessity when selection of Semiconductors takes place; as will become manifest as the design stages progress. Defining this parameter has one other benefit. It will enable a single Power Supply to be used in Applications which may have a diversity of DC Inputs (or Battery Voltages).

## 2. Outputs.

The number of outputs and the magnitude of voltage and current for each output – including any percentage allowed for overload.

## 3. Overall size.

This will to some extents determine the switching frequency, as will -

## 4. Transient Response Time.

Does such a parameter exist within the overall specification for the Power Supply (PSU).

## 5. Switch Frequency.

This is for the regulator.

## 6. Input to Output Isolation.

Is this a necessity?

For the purposes of this application note it will assumed that isolation will always be a requirement.

Having established the above criteria it is now essential to first consider **the minimum mass of the isolation transformer**. For this exercise the total Power Throughput ( $P_T$ ) must be established. The Power Throughput is the sum of all the output power levels of the various outputs – which must include the allowance for overloads viz –  $P_O = E_O * I_O * overload factor$  (i.e. 1.1 would be the overload factor for a 10% overload requirement) and where  $E_O$  and  $I_O$  are the DC values of Output Voltage and Output Current. If we assume no more than three outputs then –

$$P_T = P_{01} + P_{02} + P_{03}$$

The total Energy Transfer ( $E_T$ ) for each switching cycle will therefore equate to  $P_T/f_{SW}$  – where  $f_{SW}$  is the Switching Frequency of the Regulator. *And Switch Frequency should be the very next variable to be considered*. In most instances a frequency not greater than 100kHz should prove to be perfectly adequate for any eventuality – without incurring the penalty of ever increasing switching losses.

Having determined the switch frequency the Minimum Mass (M<sub>MIN</sub>) of the transformer can now be determined by empirically using a core energy transfer factor (C<sub>F</sub>) between 50 and 80 micro-joules, of energy transfer, per gram of core material. We can now set down the first equation, which is the Minimum Mass for the isolation transformer in grams -

$$M_{MIN} = E_T \div C_F \tag{1}$$

The next task is the determination of the Power Switch's Blocking Voltage Capability BV<sub>DSS</sub> and it's Continuous Current {ip(CONT)}. For this purpose it is necessary to know the Continuous Input Voltage Range (Max to Min). This is the voltage range, of inputs, over which the supply can work without any changes being made to any of the components. For the purposes of this Note the worst-case scenario will be used where the Continuous Input Voltage Range is 24VDC (nominal) to 48VDC (nominal) - an exceedingly wide range of inputs by any standard. For this Battery input voltage range certain assumptions must be made. At 24V input the battery voltage may fall to as little as 12V {eIN(MIN)} with the power supply being expected to still be fully functional; while also being expected to be fully functional for a nominal battery voltage of 48V during charging - which in the case of Lead-Acid batteries will be as high as 58VDC {e<sub>IN(MAX)</sub>}. The final input voltage range will therefore be seen to be 58:12 or 4.83:1. To have made the Supply capable of operating from a Battery range of 12V{6Ve<sub>IN(MIN)</sub>} to 48V, although still feasible, would not be economic.

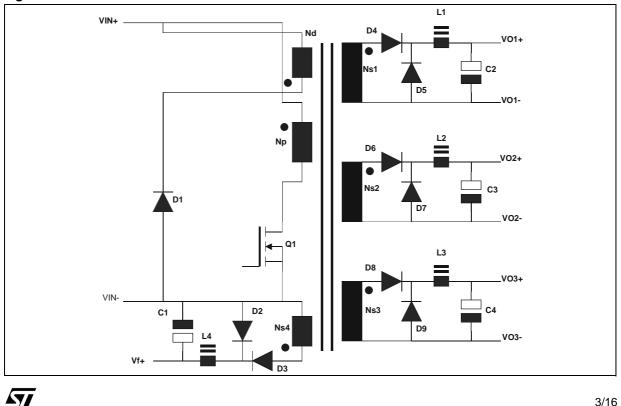

In determining the BV<sub>DSS</sub> of the Power Switch it is therefore necessary to consider which of the two alternative converter topologies will be used. The application note assumes the two topologies to be The Single-ended Forward Converter and The Single-ended Fly-back Converter. Simplified Schematics for both versions are given in figures 1(a) and (b).

**Figure 1a: Forward Converter**

In the 'forward converter' schematic the Diode D1 along with the transformer winding  $N_D$  is used to 'demagnetize' the transformer core of residual energy thereby enabling the transformer to reset to 'Remanence' during the time Switch Q1 is 'Off'.

#### Figure 1b: Flyback Converter

What should be apparent from the two drawings is the lack of the 'averaging inductor' in each of the secondary circuits in figure 1b. This is achieved by utilizing a phase reversal in the secondary windings of the transformer as can be seen in figures 1(a) and 1(b). {The starts of all windings, in the schematics of 1(a) and 1(b) are denoted by a spot.} This results from the fact that, in 1(b), energy, stored during the time Q1 was 'On', is transferred from primary to secondary during the 'fly-back stroke' of the converter – thereby demagnetizing the core. It will also be seen that the schematic of figure 1(a) shows the converter with a 'demagnetization' winding - if economy in Q1 selection is of less significance than overall performance.

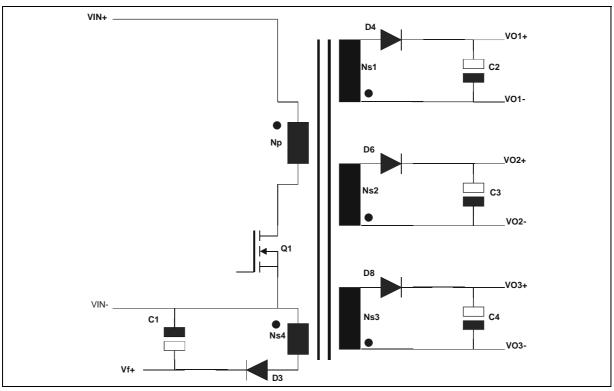

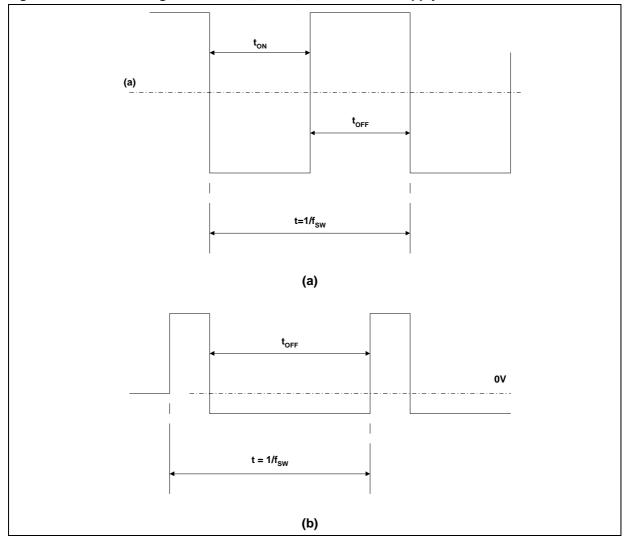

#### 4. DETERMINING BV<sub>DSS</sub> FOR Q1 WITHOUT TRANSFORMER DEMAGNETISATION.

Let us first consider the switch for a 'Forward' topology; while at the same time minimizing the breakdown voltage rating for the MOSFET for reasons of economy. In this instance balancing the volt-second products to which the transformer is exposed, during  $t_{ON}$  (the 'On' time) and  $t_{OFF}$  (the 'Off' time) of Q1, is an absolute necessity. This is best seen in the waveform of the voltages, which appears across the primary of the transformer and which is shown in the drawing of figure 2.

<u>ل</u>رکا

Figure 2: Idealized Voltage Waveforms, for Q1, In a 'Forward' Supply

In this instance, balancing of the volt-second product will become essential at  $e_{IN(MIN)}$  when the converter will need to be operating at 50% 'Duty Cycle' (when  $t_{ON}$  and  $t_{OFF}$  are equal). When – VIN =  $e_{IN(MAX)}$  will be the time that Duty Cycle needs be limited to  $2^*e_{IN(MIN)} \div e_{IN(MAX)}$  (expressed as a ratio) if transient load changes are to be accommodated. It can therefore be seen that 20% Duty Cycle is all that can be tolerated {@  $e_{IN(MAX)}$ } if transformer Core Saturation is to be avoided. The primary voltage waveform for this condition is given in figure 2(b). It can, therefore be seen from figure 2(b) that during  $t_{OFF}$  the magnitude of the reverse voltage across the transformer primary will be equal to ¼ that of  $e_{IN(MAX)}$ . The implication (if no allowance is made for 'Leakage Inductance' and transients) is that  $BV_{DSS}$ , for Q1 can be shown to be –

$$BV_{DSS} \approx e_{IN(MIN)} + \{2 \times e_{IN(MIN)}\}$$

(2)

Therefore, for  $e_{IN(MAX)} = 58VDC$ ,  $BV_{DSS}$  will need be no greater than 75V which will enable a 100V MOSFET to be used in the position for Q1.

When the topology is that of the 'Flyback' determining the  $BV_{DSS}$  will be seen to be significantly easier – because of the 'clamping' action of the output capacitors on the secondary windings and the turns-ratio of those same secondary windings which will have been determined when  $V_{IN}=e_{IN(MIN)}$ . Then, since it is necessary to balance the volt-second products at  $e_{IN(MIN)}$ , it will be seen that  $BV_{DSS}$ , of Q1, will be equal to  $e_{IN(MAX)} + e_{IN(MIN)}$ . Which will show that the voltage rating of the MOSFET will need to be equal to 58V + 6V = 64V. Again a 100V rated MOSFET will be seen to be perfectly viable.

#### 4. DETERMINING THE BREAKDOWN VOLTAGE RATINGS OF THE SECONDARY RECTIFIERS.

#### 4.1 'Forward' Converter Variant.

Let us first establish the turns ratios of the transformer windings when VIN=eIN(MIN). It can be shown that:

$$Np = 2 \times e_{IN(MIN)} \div \{f_{SW} \times Ae \times \delta\beta\}$$

(3)

Where Ae is the effective core area (in square meters), which can be found from the core's data and  $\delta\beta$  is the usable flux density (in Teslas) which can also be found from the core's data. In this instance it will be seen that  $\delta\beta$  will be less than  $\beta$ SAT -  $\beta$ REM (both figures relating to 100°C Core Temperature) where  $\beta$ SAT and  $\beta$ REM are the flux densities at Core Saturation and Remanence respectively.

It is now necessary to determine the number of turns each of the secondary windings will require. In order to do this it is first necessary to determine the peak voltage  $\hat{e}_{(Ns)}$  which will appear across the winding during  $t_{ON}$ .

It can be shown that  $\hat{e}_{(Ns)} = 2 * V_O + V_{f(d)}$ , where  $V_O$  is the DC value for the output voltage and  $V_{f(d)}$  is the forward volt-drop of the rectifier diode.

It can therefore be seen that:

$$Ns = 2 \times \{V_o + V_{f(d)}\} \times Np \div e_{IN(MIN)}$$

The three equations relating to the Core Mass and the number of turns for the primary and each of the secondary windings are all that will be given here. This note is not meant to be a design course in transformer magnetics. If the design of the transformer is beyond the expertise of the OEM designer, then it is suggested the expertise of a transformer supplier be sought.

But the real value of  $v_{RRM}$ , the maximum applied reverse voltage for the diode will occur when  $V_{IN}=e_{IN(MAX)}$  when  $\hat{e}_{(NS)}$  during  $t_{OFF}$  will be equal to the sum of  $V_O$  and  $e_{IN(MAX)}+(2^*e_{IN(MIN)})^*Ns+Np$  viz.

$$v_{RRM} = V_o + \{e_{IN(MIN)} + [2 \times e_{IN(MAX)}]\} \times Ns \div Np$$

(5)

This voltage rating only applies to the rectifier; i.e. D3, D4, D6 and finally D8. For the 'freewheeling' diodes D2, D5, D7 and D9.

$$v_{RRM} = \{e_{IN(MIN)} + [2 \times e_{IN(MAX)}]\} \times Ns \div Np$$

(6)

#### 4.2 Flyback Converter.

The voltage rating of any individual rectifier will be found to be the same as that for the 'forward' version of the power supply. It is only when it comes to the individual rectifiers' current ratings that we see a significant difference.

# 5. DETERMINING CURRENT RATINGS FOR THE SEMICONDUCTORS IN EACH VARIANT OF THE POWER SUPPLY.

#### $I_{D(CONT)}$ for the MOSFET in the 'Forward Converter' variant

An examination of the schematic of figure 1(a) will show that the peak value of current flowing through any one of the rectifiers will equate to that of it's own individual output. It can therefore be seen that the peak value of  $I_D$  will therefore be the sum of those outputs – but referred to the primary of the transformer by the respective turns ratios. viz.  $\hat{I}_D = I_{O(1)} N_{S1} N_P + I_{O(2)} N_{S2} N_P + I_{O(3)} N_{S3} N_P + I_{O(4)} N_{S4} N_P$ . This can, in turn, be written as:

$$\mathbf{\hat{I}}_{D} = \{I_{o(1)} \times N_{s(1)} + I_{o(2)} \times N_{s(2)} + I_{o(3)} \times N_{s(3)} + I_{o(4)} \times N_{s(4)}\} \div Np$$

But this will only give the peak value of I<sub>D</sub>. To determine the continuous rating one must now translate the peak value into the RMS value and this will be seen to be:

$$I_{D(CONT)} = \left\{ \left| \hat{\mathbf{i}}_{D}^{2} \times DR \right\}^{1/2}$$

(7)

Where DR is the duty ratio of the switching cycle. It can be seen that the worst case value will occur when DR = 0.5 or when  $V_{IN} = e_{IN(MIN)}$ .

#### 6. I<sub>D(CONT)</sub> FOR THE MOSFET IN THE 'FLYBACK CONVERTER' VARIANT.

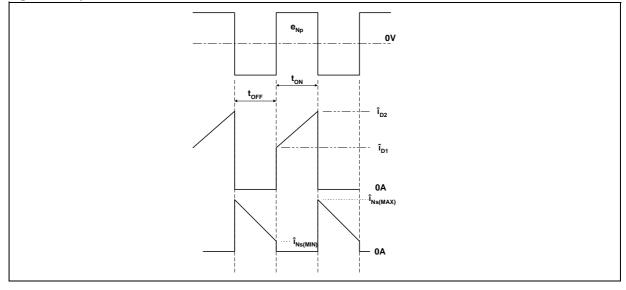

In determining this parameter it is essential to momentarily forget the various turns ratios and consider only, the energy, which must be generated (then stored) within the core of the transformer. To do so it is necessary to examine the waveforms in figure 3.

#### Figure 3: Flyback Current Waveforms

From the idealized waveforms it can be seen that the converter is operating in the 'Continuous Mode' and that at the near-instant of Q1 'turning on'  $\hat{i}_D$  will initially be set to  $\hat{i}_{D1}$ , then progressively ramp up to  $\hat{i}_{D2}$  which occurs at the time when Q1 begins 'turning off'. This 'ramping-up' will be seen to be due to the magnetizing of the transformer core – viz energy is being stored in the core. This energy can be expressed as:

$$E_{Np} = (1/2) \times L_{MAG(Np)} \times \{ \hat{\mathbf{1}}_{D2}^2 - \hat{\mathbf{1}}_{D1}^2 \}$$

Where  $L_{MAG(Np)}$  is the transformer's **Magnetizing Inductance** referred to the Primary Winding. But  $E_{Np}$  can also be shown to be equal to the sums of the energies that will be passed via each of the secondaries during t<sub>OFF</sub> viz.

$$E_{Np} = (1/2) \times [L_{MAG(Ns1)} \times \{I_{Ns1(MAX)}^{2} - I_{Ns1(MIN)}^{2}\} + \dots]$$

$$\dots L_{MAG(Ns2)} \times \{I_{Ns2(MAX)}^{2} - I_{Ns2(MIN)}^{2}\} + \dots$$

$$L_{MAG(NsN)} \times \{I_{NsN(MAX)}^{2} - I_{NsnN(MIN)}^{2}\}]$$

If we express the sums of the products within the square brackets  $\{[]\}$  as 'Secondary Energies' and equate both sides of  $E_{Np}$  we can then see that:

$$\hat{\mathbf{1}}_{D2}^{2} - \hat{\mathbf{1}}_{D1}^{2} = (SecondaryEnergies) \div L_{MAG(Np)}$$

But  ${I_{D2}}^2 - {I_{D1}}^2 = {}^{1\!\!\!/}_2 * \hat{\imath}_{D(ON)} * \delta \, \hat{\imath}_{D[t(ON)]},$  where:

$$\delta \hat{\mathbf{i}}_{D[t(ON)]} = V_{IN} \times t_{ON} \div L_{MAG(Np)}$$

We can, therefore, express  $\hat{i}_{D(ON)}$  as:

$$I_{D(ON)} = 2 \times SecondaryEnergies \div (V_{IN} \times t_{ON})$$

but each of the 'Secondary Energies' can be shown to be equal to the output power of each output for the duration of one switching cycle ( $t_{ON}+t_{OFF}$ ) OR 1/ $f_{SW}$ . We can, therefore, express  $I_{D(ON)}$  as:

$$I_{D(ON)} = 2 \times f_{SW} \times (P_{O1} + P_{O2} + P_{O3} + P_{O4}) \div (V_{IN} \times t_{ON})$$

which can in turn be expressed as:

$$I_{D(ON)} = 2 \times (P_T) \div (VIN \times DR)$$

$I_{D(ON)}$  is  $\hat{i}_D$  averaged over  $t_{ON}$ .

Therefore:

$$I_{D(CONT)} = \{I_{D(ON)}^{2} \times DR\} \quad or$$

$$I_{D(CONT)} = 2 \times P_{T} \div \{VIN \times (DR)^{1/2}\} \quad (8)$$

#### 7. CURRENT RATINGS OF THE RECTIFIERS.

#### 7.1 'Forward Converter' Power Supply.

The four rectifiers (D3, D4, D6 and D8) can each be shown to have an average current rating requirement, which is equal to half that of each rectifier's respective output. This factor arises out of each rectifier never conducting for more than 50% of the available time for each switch cycle.

For example, D4 will require an average current handling capability  $I_{F(AVE)}$  that is equal to half that of  $I_{O1}$ . On the other hand, it will be seen that within the same topology, of Power Supply, the freewheeling diodes (D2, D5, D7 and D9) will all have an average current handling capability requirement that is equal to each of their respective output current ratings. The reason for this lies in the fact that each 'freewheeling' device, could (because of current limit requirements) have to conduct over more than 95% of each and every switch cycle.

#### 7.2 'Flyback' Variant Of The Power Supply.

Each of the transformer secondaries will pass a pulse of energy that must include the current, for it's output, for the complete switch cycle. Since the voltage of each secondary will be clamped to its output, it will be seen that the magnitude of the current pulse will be twice that which will flow out of the output terminals.

$$(1/2) \times \{I_{Ns(MAX)} + I_{Ns(MIN)}\} = 2 \times I_O$$

The implication, in this instance, is the rectifier requiring an average current rating  $I_{F(AVE)}$  that is equal to the DC Output but where that current will only flow for a period in time that does not equate to the whole of the switch cycle; i.e the rectifier's current waveform will have a 'Crest (Form) Factor' of 2 or greater.

But this is not the only factor, which must be taken into account. There is the RMS current  $I_{F(RMS)}$  to consider as well and this can be expressed as:

$$I_{F(RMS)} = \left[\left\{I_{Ns(MAX)}^{2} + I_{Ns(MIN)}^{2}\right\}/2 \times DR\right]^{1/2}$$

(9)

By way of example – Consider a 'Flyback' Supply's 5V/5A output. Let  $I_{Ns(MIN)}$  be 5 and let  $I_{Ns(MAX)}$  be 15 and let DR be 50%.

Using (9) we get I<sub>F(RMS)</sub> = 7.91A.

In contrast, a Forward Supply's rectifier for the same output current and Duty Cycle would have an RMS current of 3.54A. This increase in the RMS current, which a Flyback Supply's rectifier must handle, can be shown to possibly affect System Reliability since the Form Factor of a rectifier can be shown to be a 'Stress Factor' and should be taken into account when deciding on the topology.

Because of this increase in  $I_{F(RMS)}$ , and the subsequent heating effect of a poor 'Form Factor' additional losses will result. To facilitate the calculation of these losses an equation will usually be found within the rectifier's datasheet, which will enable the additional losses to be calculated.

#### 8. RULES FOR COMPONENT SELECTION.

When it comes to component selection it is advisable to begin by considering the losses that would be acceptable for each device – on an economic basis. For example, simply picking the lowest  $R_{DS[ON]}$  MOSFET, for Q1, within the  $BV_{DSS}$  band might well be good for overall efficiency while making the supply economically untenable. It is this reasoning which makes this section an integral part of the application note. Let us start with the losses, which one can reasonably expect to sustain with each component. For rectifiers let us first consider 5V outputs since it is here that the highest losses will be sustained (up to 10%) - unless 'Synchronous Rectifiers' are considered. But, since this is not an option for this Sample Kit Application Note, let us consider Schottky Rectifiers. *Always select a Schottky with a*  $v_{RRM}$  rating that satisfies (5) if it is the rectifier and (6) when it is the freewheel diode. DO NOT OVER-SPECIFY. Then within the desired Voltage Ratings, select devices with the lowest  $v_{(F)}$  @ the currents defined under the paragraph 'CURRENT RATINGS.... RECTIFIERS For the Forward Converter Power Supply'.

Let us consider higher voltage output rectifiers next. If (5) and (6) can be satisfied by using Schottky Rectifiers then do so otherwise select devices that are also blessed with the lowest possible  $t_{rr}$  (Reverse-Recovery Time) thereby minimizing 'Switching' Losses.

Let us finally consider the device for Q1. For this socket experience will show that losses  $\leq 5\%$  of the throughput power can be considered as being economically acceptable. Then **using**  $I_{D(CONT)}$  from (7) or (8) and with Conduction Losses of Q1 { $P_{(Q1)} \approx 0.045 * P_T$ } select for  $R_{DS[ON]}$ .

#### 9. AVERAGING INDUCTORS FOR A FORWARD POWER SUPPLY.

Specifying the inductors L1 to L4 can be achieved by considering the '**ripple current**', which will flow through each of the inductors. These ripple currents are empirically determined to have an RMS value equal to between 10% and 20% of the respective Output Current. It then becomes necessary to convert this level of ripple current to a peak value ( $I_{RIPPLE}$ ). Therefore  $I_{RIPPLE}$  can be shown to equate to  $I_{RIPPLE(RMS)} * \sqrt{2}$ . Since  $I_{RIPPLE}$  is intrinsically triangular in shape and using e\*t=L\*I - (e =  $\int L di/dt$  integrated) we can show each individual inductor to be:

$$L = \{ [e_{IN(MAX)} \times N_s / N_P] - VO \} \times t_{ON} \div I_{RIPPLE}$$

(10)

The supplier of the transformer should also be able to supply the inductor(s) provided it is stipulated that the inductance {from (10)} should be at the rated output current. For improved cost and 'Power Trading' all of the inductors could well be accommodated on a single core.

## 10. LAYOUT.

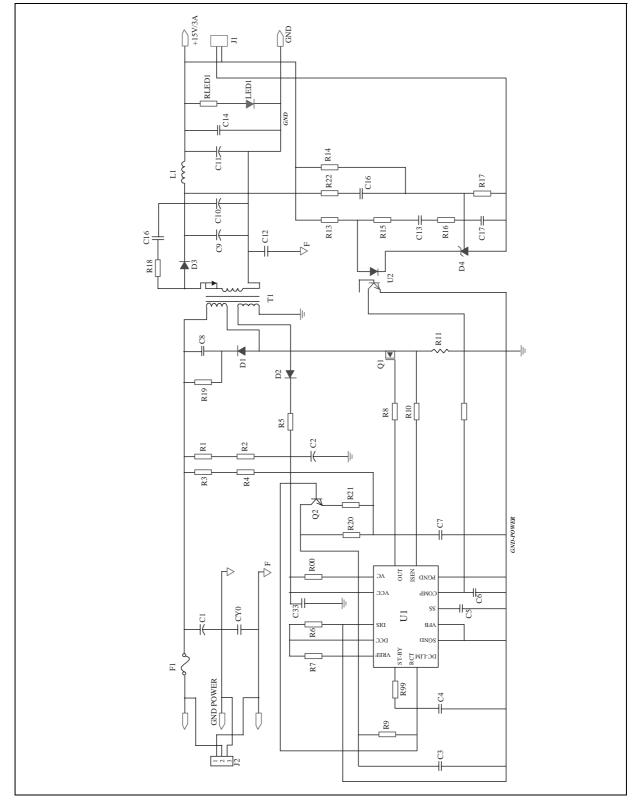

## Figure 4: Circuit Layout

Layout of the Power Circuit should follow what is considered as being good practice for MOSFET circuits – even if today's FETs have sufficient avalanche capability to protect themselves against transients. The reason for good layout is to prevent unwanted spikes and transients from having to be absorbed by Q1, since the device is already being called on to absorb the energy in the 'Leakage Inductance' of the transformer. But what exactly is meant by good layout? This can best be summarized as follows:

- 1. Keep all power leads as short as is physically possible.

- 2. Ensure the power circuit is as compact as possible.

- 3. Minimize the dimension between the gate-drive circuit and the gate of Q1.

4. Physically connect the return of the gate-drive circuit to the source pad of Q1. Do not be tempted to connect this return to the nearest part of the power circuit, which corresponds to a connection to the source of Q1.

5. Ensure the transformer is mounted in such a position as to minimize 'flux' coupling to the Printed Circuit Board (PCB) tracks.

6. Use the heaviest copper grade available for the PCB. Remember there could be several amperes of current flowing in the Power tracks. Also make sure the power tracks are as wide as is physically possible, commensurate with a compact layout.

7. Above all else remember one centimeter of copper approximates to 10nH of inductance.

But this note isn't simply about the design rules of Switch Mode regulators alone. There is a 'Sample kit', which is a fundamental part of the scheme. To enable the sample kit to be evaluated three sets of tables will be found at the end of the application note. These tables show the semiconductors, which will be required for three completely different solutions. They provide a means of rapid selection of a solution, which should satisfy a wide range of applications.

Though it should be noted that use of the three tables will not provide for the transformer selection. If this is required then it is recommended the evaluator use the recommended list of components to populate the evaluation circuit board.

## 11. CONCLUSION.

Having defined the ground rules for simplified Power Supply design, one is tempted to beg the question as to why an OEM user would find such a solution, as outlined in this application note, to be particularly desirable. There are several reasons to support such a choice. These may be qualified thus –

1. Although the solutions are not 'cut and dried' (and complete), which no application note solution should ever be treated as being, the solutions offered here do provide tried and tested ground rules for Power Supplies that are easily designed to be virtually as good as many which can be purchased from specialist Vendors.

2. With component selection coming from a vendor with the widest portfolio of cutting edge technology and benchmark products. This can be extended to include –

3. Purchasing the complete set of semiconductor components could not be easier; since ST offers a 'One-stop Shopping' opportunity for the supply's semiconductors, including Pulse Width Modulation control – whether this control is delivered in the shape of a conventional PWM IC or micro-controller.

**ل ۲**ک

#### 12. ADDENDUM.

#### 12.1 Demonstration Sample Kit.

An application note, regardless as to how good it may be, cannot be a real substitute for practical examples and it is for that very reason that the Demonstration Sample Kit has been made available. This kit will enable the less experienced engineer to see for himself as to how well the rules (that have been laid out) apply to a working design. In order for a Sample Kit to be workable reality it is necessary for a specification to be compiled, even if the specification is not wholly complete. A brief specification for a wide input range, battery supplied DC-DC Converter is given below:

Input = 24V to 48V DC (Nominal) 18V to 58V DC (Actual) Output = 15V ± 0.5V DC @ 3A Regulation = ±2% from Min to Max Load Target Efficiency = 80% Frequency = 150kHz

Since the specified Output Power is only 45W, it was felt the topology of the demonstration converter should be a flyback and a full copy of the schematic is given in figure 4.(at the very end of this document).

The Transformer's Core Mass of 24 grams will be found to conform quite adequately to that which would be determined by the use of Equation 1 if  $E_T$  equates to 300µJoules and a Core Factor of 50µJoules per gram is used. From the use of (1) the Minimum Mass would be 6 grams the selected EFD30 Core provides a superior Window over any other core of a more suitable Mass. With a Primary Inductance  $(L_{MAG})$  of 5.76µH (from a suitably gapped core) and an actual switch frequency of 170kHz; and using  $E_{Np} = \frac{1}{2} \cdot L_{MAG} \cdot I_{D2}^2 - I_{D1}^2$  the Continuous Current Rating { $I_{D(ON)}$ } of the Switch Q1 can be found to be approximately equal to 6.2A. So that the losses in Q1 are not excessive for the 9°C/W Heatsink a STP50NE10 has been selected for the socket of Q1. The chosen PWM IC is the L5991 with the Schottky output rectifier (STPS8H100D) chosen so efficiency can be maximized.

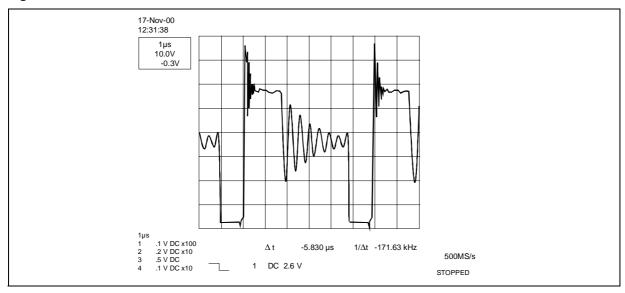

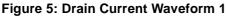

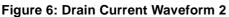

The operating waveform for the Drain Voltage of Q1, for a light load of approximately ½ an Ampere and a DC Supply of 35V can be seen in figure 5 (above). The ringing at the termination of rectifier conduction is normal and should not be of any concern to the would be user. A similar waveform for the same input voltage but for an output current of approximately 1 Ampere is given in figure 6 (below).

Before building the demonstration DC-DC converter it is strongly recommended that the schematic is thoroughly studied along with the enclosed '**Component List**' and the accompanying tips, which are related to the assembly of the circuit board.

## 12.2 PC Board Assembly Tips.

When the time comes to assemble the Sample PCB always ensure the smallest components are fitted first. These components will be found to be most of the resistors and a few of the lower value capacitors. It is also advisable to work from the middle outwards.

When it comes to fitting the two heatsink mounted semiconductors do make sure the MOSFET is mounted on the sink to which the **Kapton** pad has been applied. Do also make sure a suitable **Thermal Grease** is smeared on the lower surface of the TO-220 tabs. Clip the two semiconductors to their respective heatsinks then mount sinks and components on to the PCB before finally soldering the parts in place. Ensure all solder joints have been adequately wetted and do not allow the soldering iron to overheat the semiconductor pins.

During the fitting of Q1 do ensure not to pick up the part by any or all of the three leads. Hold the MOSFET by the exposed tab. If at all possible use a wrist-grounding strap to ensure damage due to ESD is avoided. This last tip also applies to the Schottky Rectifier.

5

Do make sure all Electrolytic Capacitors are mounted such that their polarity conforms with accepted practice viz. observe the negative silk-screen symbol on the PCB.

An additional feature, to be found on the PCB, is the many holes at the lower right and lower left extremities of the board. These holes could enable the user to use them as a 'patchwork' board for easy prototyping of any additional circuitry, which may be required to complement the Converter or as a standalone function in its own right.

## 13. DC/DC APPLICATION SAMPLE KIT - BILL OF MATERIAL.

#### 13.1 Capacitors.

- C1 Capacitor Electrolytic 2200\_F 63VDC Wkg

- C2 Capacitor Electrolytic 100\_F 35VDC Wkg

- C3 Capacitor Polyester 0.1\_F 63VDC Wkg

- C4 Capacitor Ceramic 470pF 100VDC Wkg

- C5 Capacitor Polyester 68nF 63VDC Wkg

- C6 Capacitor Polyester 1nF 100VDC Wkg

- C7 Capacitor Ceramic 220pF 100VDC Wkg

- C8 Capacitor Polyester 33nF 400VDC Wkg

- C9 Capacitor Electrolytic 1000\_F 25VDC Wkg

- C10 Capacitor Electrolytic 1000\_F 25VDC Wkg

- C11 Capacitor Electrolytic 1000\_F 25VDC Wkg

- C12 Capacitor Disc Ceramic 4-7nF 4KVDC Wkg

- CYO Capacitor Polyester 4.7nF 400VDC Wkg

- C13 Capacitor Ceramic 0.1\_F 100VDC Wkg

- C14 Capacitor Ceramic 0.1\_F 100VDC Wkg

- C15 Capacitor Ceramic 0.1\_F 100VDC Wkg

- C16 Capacitor Ceramic 1nF 100VDC Wkg

- C17 Capacitor Ceramic 1nF 100VDC Wkg

- C33 Capacitor Ceramic 220nF 50VDC Wkg

## 13.2 Resistors.

- R00 Resistor 0

- R1 Resistor\_W 2K2

- R2 Resistor\_W 2K2

- R3 Resistor\_W 150K

- R4 Resistor\_W 150K

- R5 Resistor W 15

- R6 Resistor\_W 5K6

- R7 Resistor\_W 4K3

- R8 Resistor\_W 1.0

- R9 Resistor\_W 18K

- R10 Resistor W1K

- R11 Resistor Wirewound 4W 22 milli-ohm

- R12 Resistor\_W 47\_

#### 13.3 Inductors.

L1 - Inductor 1\_H. Made up of 9 turns of 0.7mm Winding wire wound on Powder Iron Core - Type Number TN7 .5/.4.1/3-2P40 Philips.

T1 - Transformer

R13 - Resistor\_W 1K R14 - Resistor\_W 11K R15 - Resistor\_W 1K R16 - Resistor\_W 6K8 R17 - Resistor\_W 2K2 R18 - Resistor\_W 10\_ R19 - Resistor Wirewound 5W 1K R20 - Resistor\_W 7K8 R21 - Resistor\_W 7K8 R22 - Resistor\_W 6K8 R22 - Resistor\_W 1K5 RLED1 - Resistor\_W 4K7 R99 - Resistor\_W 100M

#### 13.4 Semiconductors.

|                                    | LED1 - Green               |

|------------------------------------|----------------------------|

| D1 - Rectifier Diode BYW100-200    |                            |

| D2 - Redtifier Diode BYW100-200    |                            |

| D3 - Schottky Rectifier STPS8H100D |                            |

| D4 - Voltage Reference TL431CZ     | U1 - PWM Control IC L5991  |

|                                    | U2 - Opto-coupler CYN17F-3 |

| <b>13.5 PC Board.</b><br>1 off     |                            |

LED1 Croop

## 13.6 Connectors.

J1 - 2Pin (CON 2) J2 - 3Pin (CON 1) F1 - Fuse holder and fuse (6A) - Optional, not supplied - Use wire link

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics - Printed in Italy - All rights reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

**ل ۲**